7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 187

UG482 (v1.9) December 19, 2016

RX Elastic Buffer

Ports and Attributes

Table 4-33 defines the RX buffer ports.

Table 4-34 defines the RX buffer attributes.

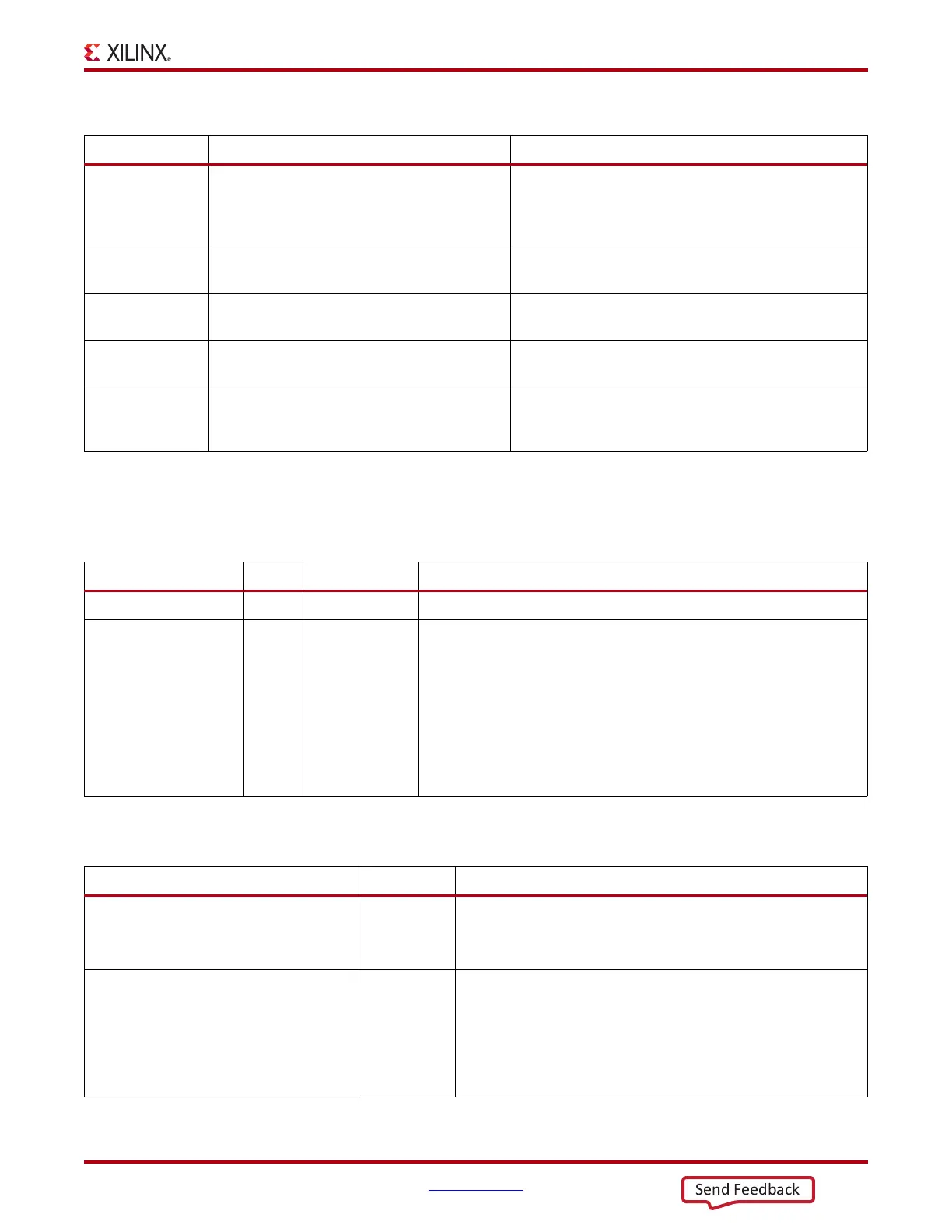

Table 4-32: RX Buffering versus Phase Alignment

RX Elastic Buffer RX Phase Alignment

Ease of Use The RX buffer is the recommended default to use

when possible. It is robust and easier to operate.

Phase alignment is an advanced feature that requires extra

logic and additional constraints on clock sources.

RXOUTCLKSEL must select the RX recovered clock as

the source of RXOUTCLK to drive RXUSRCLK.

Clocking Options Can use RX recovered clock or local clock (with

clock correction).

Must use the RX recovered clock.

Initialization Works immediately. Must wait for all clocks to stabilize before performing the

RX phase and delay alignment procedure.

Latency Buffer latency depends on features use, such as

clock correction and channel bonding.

Lower deterministic latency.

Clock Correction

and Channel

Bonding

Required for clock correction and channel

bonding.

Not performed inside the transceiver. Required to be

implemented in user logic.

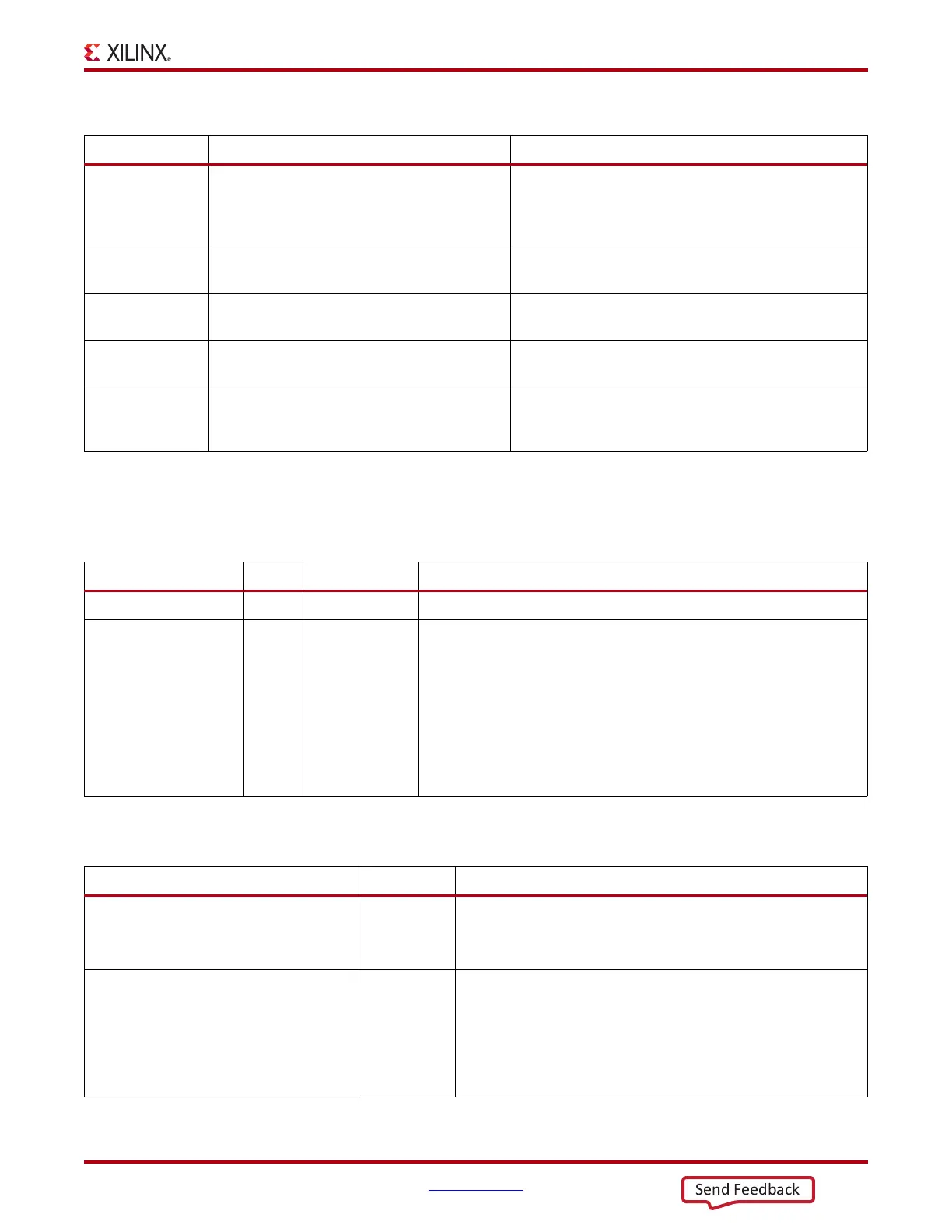

Table 4-33: RX Buffer Ports

Port Dir Clock Domain Description

RXBUFRESET In Async Resets and reinitializes the RX elastic buffer.

RXBUFSTATUS[2:0] Out RXUSRCLK2 RX buffer status.

3’b000: Nominal condition.

3’b001: Number of bytes in the buffer are less than

CLK_COR_MIN_LAT

3’b010: Number of bytes in the buffer are greater than

CLK_COR_MAX_LAT

3’b101: RX elastic buffer underflow

3’b110: RX elastic buffer overflow

Table 4-34: RX Buffer Attributes

Attribute Type Description

RXBUF_EN String Use or bypass the RX elastic buffer.

TRUE: Uses the RX elastic buffer (default).

FALSE: Bypasses the RX elastic buffer (advanced feature).

RX_XCLK_SEL String Selects the clock source used to drive the RX parallel clock domain

(XCLK).

RXREC: Selects the RX recovered clock as the source of XCLK.

Used when using the RX elastic buffer.

RXUSR: Selects RXUSRCLK as the source of XCLK. Used

when bypassing the RX elastic buffer.

Loading...

Loading...