7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 121

UG482 (v1.9) December 19, 2016

TX Receiver Detect Support for PCI Express Designs

TX Receiver Detect Support for PCI Express Designs

Functional Description

The PCI Express specification includes a feature that allows the transmitter on a given link to detect

if a receiver is present. The decision if a receiver is present is based on the rise time of TXP/TXN.

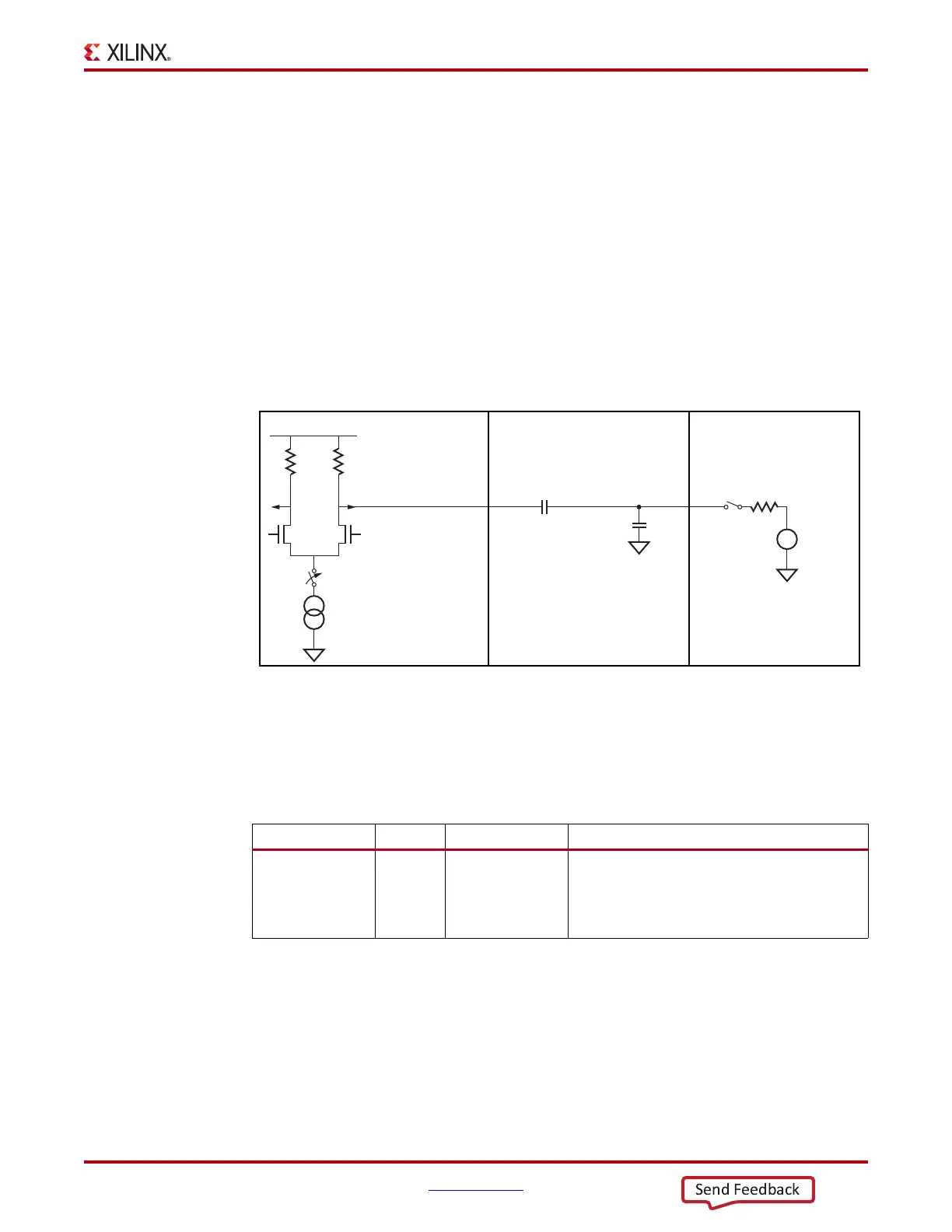

Figure 3-22 shows the circuit model used for receive detection. The GTP transceiver must be in the

P1 power down state to perform receiver detection. Receiver detection requires a 75 nF to 200 nF

external coupling capacitor between the transmitter and receiver, and the receiver must be

terminated to GND. The receiver detection sequence starts with the assertion of TXDETECTRX. In

response, the receiver detection logic drives TXN and TXP to (V

DD

- V

SWING

/2) and then releases

them. After a programmable interval, the levels of TXN and TXP are compared with a threshold

voltage. At the end of the sequence, the receiver detection status is presented on RXSTATUS when

PHYSTATUS is asserted High for one cycle.

Ports and Attributes

Table 3-30 describes the TX receiver detection ports.

X-Ref Target - Figure 3-22

Figure 3-22: Receiver Detection Circuit Model

C

CH

: < 3 nF

UG482_c3_21_110911

C

AC

: 75 nF - 200 nF

R

TERMR

: 40Ω – 60Ω

V

TERMR

R

TERMT

: 40Ω – 60Ω

V

DD

TXDETECTRX

GTP Transceiver

Components

Channel

Components

Far-End Receiver

Components

TXP

Table 3-30: TX Receiver Detection Ports

Port Dir Clock Domain Description

TXDETECTRX In TXUSRCLK2 Used to tell the GTP transceiver to begin a

receiver detection operation.

0: Normal operation.

1: Receiver detection.

Loading...

Loading...