7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 235

UG482 (v1.9) December 19, 2016

SelectIO Usage Guidelines

SelectIO Usage Guidelines

Because a GTP transceiver's performance can degrade in an environment flooded with SelectIO™

activity, it is important to have guidelines for SelectIO usage that minimize the impact on GTP

transceiver performance.

The following guidelines must be followed when routing GTP Transceiver data signals on the PCB:

• Eliminate routing of GTP Transceiver signals and SelectIO signals on adjacent layers. Be

aware of the potential of broadside coupling if these signals are routed on adjacent layers.

• Maintain isolation of the return current paths for both the SelectIO signals and the GTP

Transceiver signals including both traces and vias.

• The power islands for the GTP Transceivers are also a potential source for SelectIO induced

noise. SelectIO signals should not be routed over the GTP power islands.

Specific SelectIO Guidelines Pertaining to the FGG676 Package

• To minimize the impact to GTP performance from SelectIO in adjacent banks, SelectIO banks

16 and 35 should be avoided for line rates equal to or above 6 Gb/s.

• If SelectIO banks 16 and 35 must be used, then it is recommended to reduce the number of

SelectIOs used in these banks and the following selectIOs are prohibited:

• Bank 16: F17, F18, F20, G15, H14, H15, A17, A18, A19, B17, B19, C17, D16, D18, E16,

E18, F15, F19

• Bank 35: K8, J8, J6, J5, J4, H9, H8, H7, H6, H4, G9, G8, G7, G6, F8, F7, E6, D6

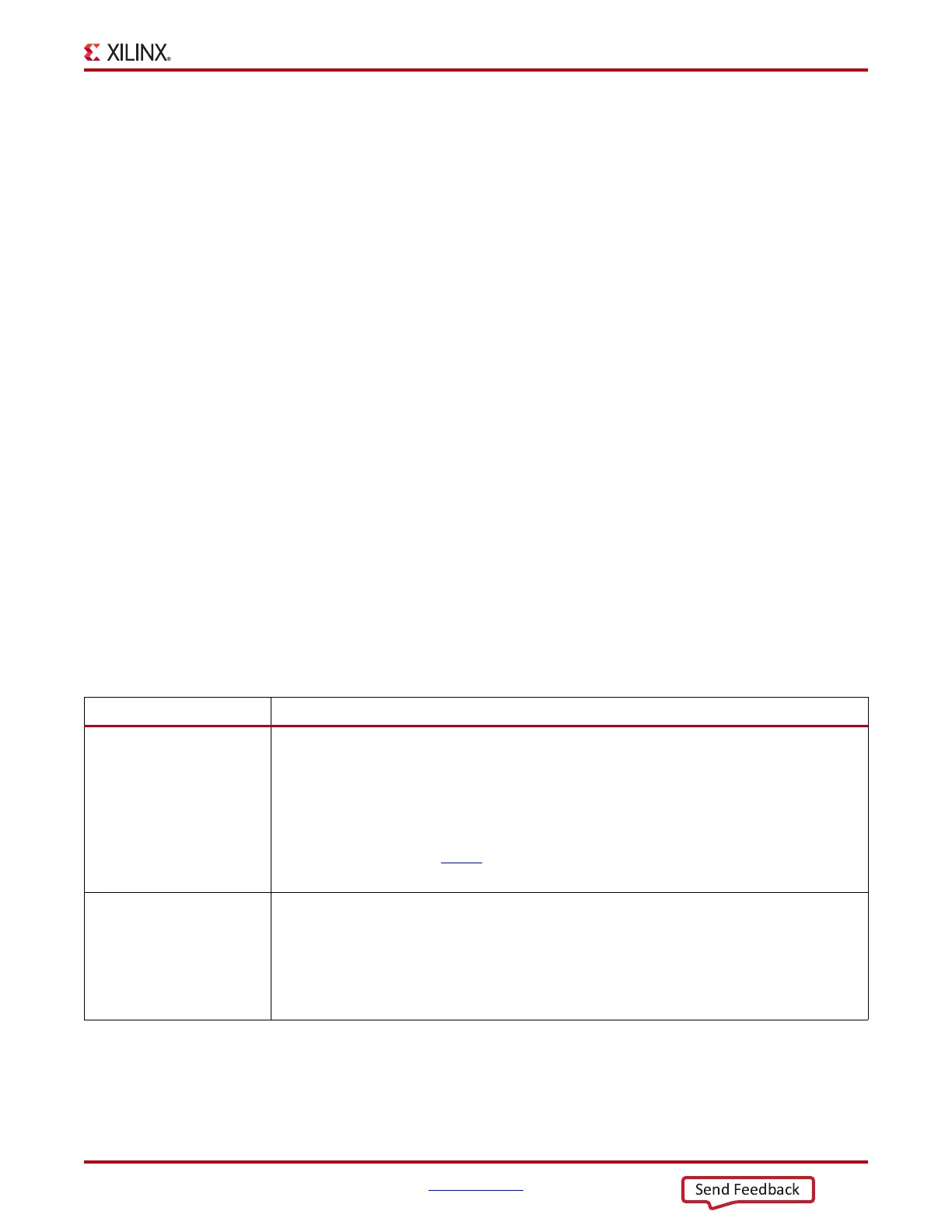

PCB Design Checklist

Table 5-14 is a checklist of items that can be used to design and review any 7-Series GTP transceiver

PCB schematic and layout.

Table 5-14: GTP PCB Design Checklist

Pins Recommendations

MGTREFCLK0P

MGTREFCLK0N

MGTREFCLK1P

MGTREFCLK1N

• Use AC coupling capacitors for connection to oscillator.

• For AC coupling capacitors, refer to Reference Clock, page 224. The recommended value for

LVD S is 100 nF.

• Reference clock traces should be provided enough clearance to eliminate crosstalk from adjacent

signals.

• Reference clock oscillator output must comply with the min/max input amplitude requirements

for these input pins. See DS181

, Artix-7 FPGAs Data Sheet: DC and Switching Characteristics.

• If reference clock input is not used leave the associated pin pair unconnected.

MGTRXP0/MGTRXN0

MGTRXP1/MGTRXN1

MGTRXP2/MGTRXN2

MGTRXP3/MGTRXN3

• Use AC coupling capacitors for connection to transmitter. The recommended value for AC

coupling capacitors is 100 nF.

• Receiver data traces should be provided enough clearance to eliminate crosstalk from adjacent

signals.

• If a receiver is not used connect the associated pin pair to ground.

•See RX Analog Front End, page 126.

Loading...

Loading...