108 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

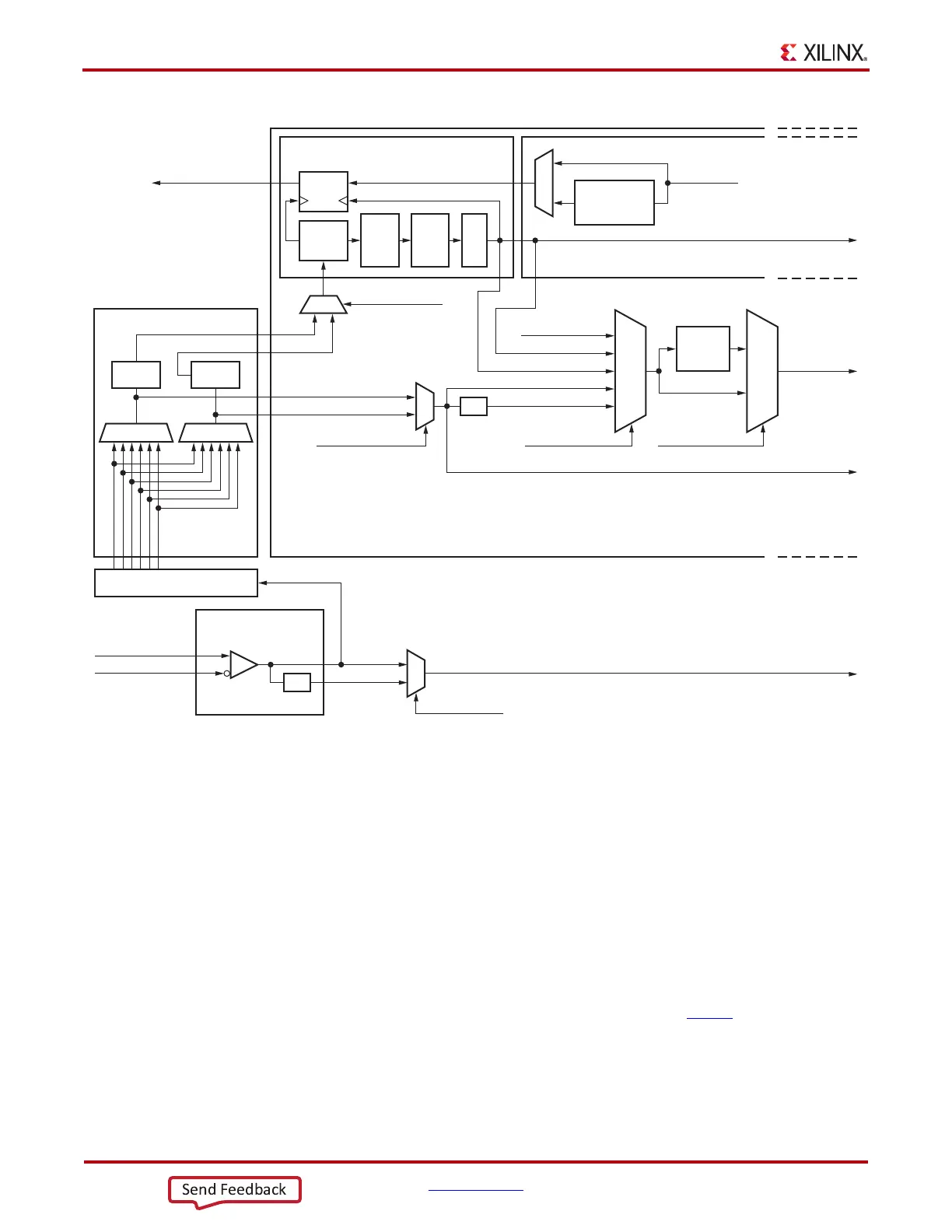

Notes relevant to Figure 3-20:

1. TXOUTCLKPCS and TXOUTCLKFABRIC are redundant outputs. Use TXOUTCLK for new

designs.

2. The REFCLK_CTRL option is controlled automatically by software and is not user selectable.

The user can only route one of the IBUFDS_GTE2’s O or ODIV2 outputs to the FPGA logic.

3. IBUFDS_GTE2 is a redundant output for additional clocking scheme flexibility.

4. The selection of the /4 or /5 divider block is controlled by the TX_DATA_WIDTH attribute

from the GTPE2_CHANNEL primitive. /4 is selected when TX_DATA_WIDTH = 16 or 32. /

5 is selected when TX_DATA_WIDTH = 20 or 40.

5. For details about placement constraints and restrictions on clocking resources (MMCME2,

PLLE2, BUFGCTRL, IBUFDS_GTE2, BUFG, etc.), refer to the UG47

2, 7Series FPGAs

Clocking Resources User Guide.

X-Ref Target - Figure 3-20

Figure 3-20: TX Serial and Parallel Clock Divider

UG482_C3_19_021113

PLL0

REFCLK Sel REFCLK Sel

GTPE2_

COMMON

GTPE2_CHANNEL (GTP Transceiver Primitive)

IBUFDS_GTE2

TX PMA

TX PCS

REFCLK Distribution

PLL1

Phase

Interp

/D

{1,2,

4,8}

PISO

/2

/2

Delay

Aligner

PLL1OUTCLK

‘1’

TXOUTCLKPCS

TXOUTCLKPMA

PLL0REFCLK

PLL1REFCLK

O

ODIV2

TXOUTCLK

TXOUTCLKPCS

1

T X DATA From

Upstream

PCS Blocks

TXPLLREFCLK_DIV1

TXPLLREFCLK_DIV2

TXOUTCLKFABRIC

1

IBUFDS_GTE2 Output to Logic

3

TXOUTCLKSELTXSYSCLKSEL[1]

REFCLK_CTRL

2

TXSYSCLKSEL[0]

TXDLYBYPASS

000

001

0

1

010

011

100

PLL0OUTCLK

1

0

1

0

1

0

/4 or

/5

/2

TXP/N TXDATA

TX Polarity

Control

MGTREFCLK[0/1]P

MGTREFCLK[0/1]N

Loading...

Loading...