7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 127

UG482 (v1.9) December 19, 2016

RX Analog Front End

Ports and Attributes

Table 4-1 defines the RX AFE ports.

Table 4-2 defines the RX AFE attributes.

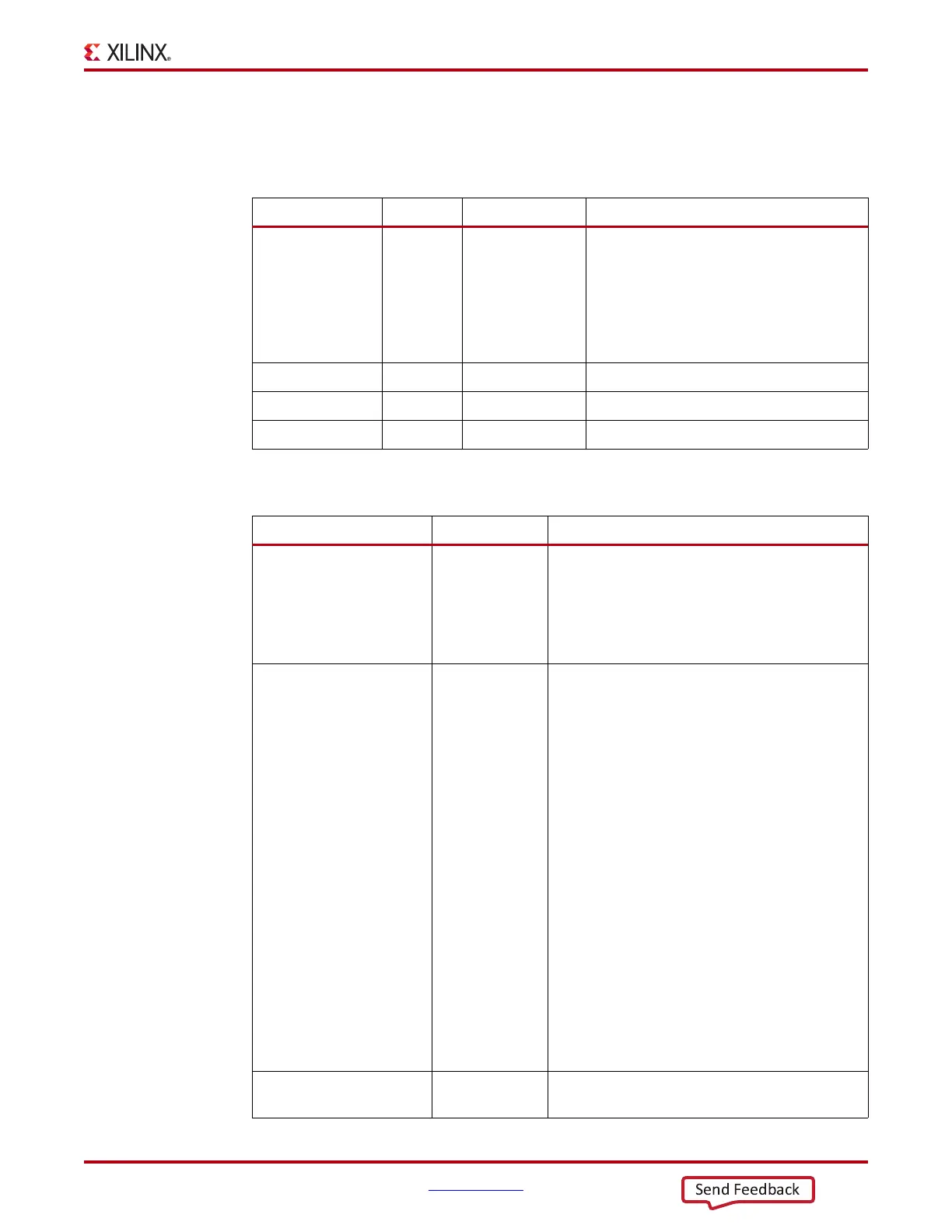

Table 4-1: RX AFE Ports

Port Dir Clock Domain Description

GTPRXN,

GTPRXP

In (Pad) RX Serial Clock GTPRXN and GTPRXP are differential

complements of one another forming a

differential receiver input pair. These ports

represent pads. The location of these ports

must be constrained (see Implementation,

page 20) and brought to the top level of the

design.

PMARSVDOUT1 Out Async Reserved.

PMARSVDOUT0 Out Async Reserved.

PMARSVDIN2 In Async Reserved.

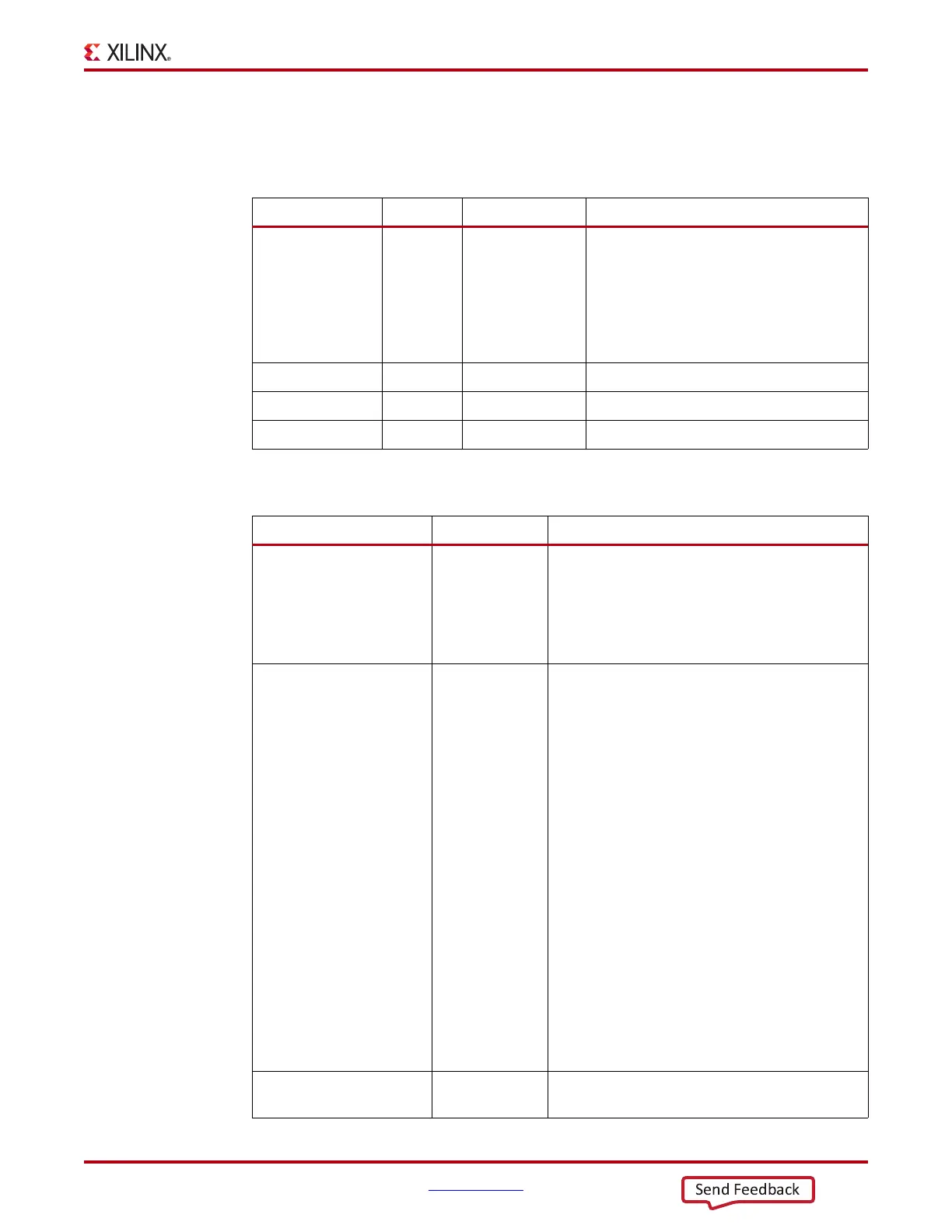

Table 4-2: RX AFE Attributes

Attribute Type Description

RX_CM_SEL [1:0] 2-bit Binary Controls the mode for the RX termination voltage.

2'b00 - AVTT

2'b01 - GND

2'b10 - Floating

2'b11 - Programmable

RX_CM_TRIM [3:0] 4-bit Binary Controls the Common mode in Programmable

mode.

4’b0000 – 100 mV

4’b0001 – 200 mV

4’b0010 – 250 mV

4’b0011 – 300 mV

4’b0100 – 350 mV

4’b0101 – 400 mV

4’b0110 – 500 mV

4’b0111 – 550 mV

4’b1000 – 600 mV

4’b1001 – 700 mV

4’b1010 – 800 mV

4’b1011 – 850 mV

4’b1100 – 900 mV

4’b1101 – 950 mV

4’b1110 – 1000 mV

4’b1111 – 1100 mV

TERM_RCAL_CFG[14:0] 15-bit Binary Controls the internal termination calibration circuit.

This feature is intended for internal use only.

Loading...

Loading...