Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 119

UG074 (v2.2) February 22, 2010

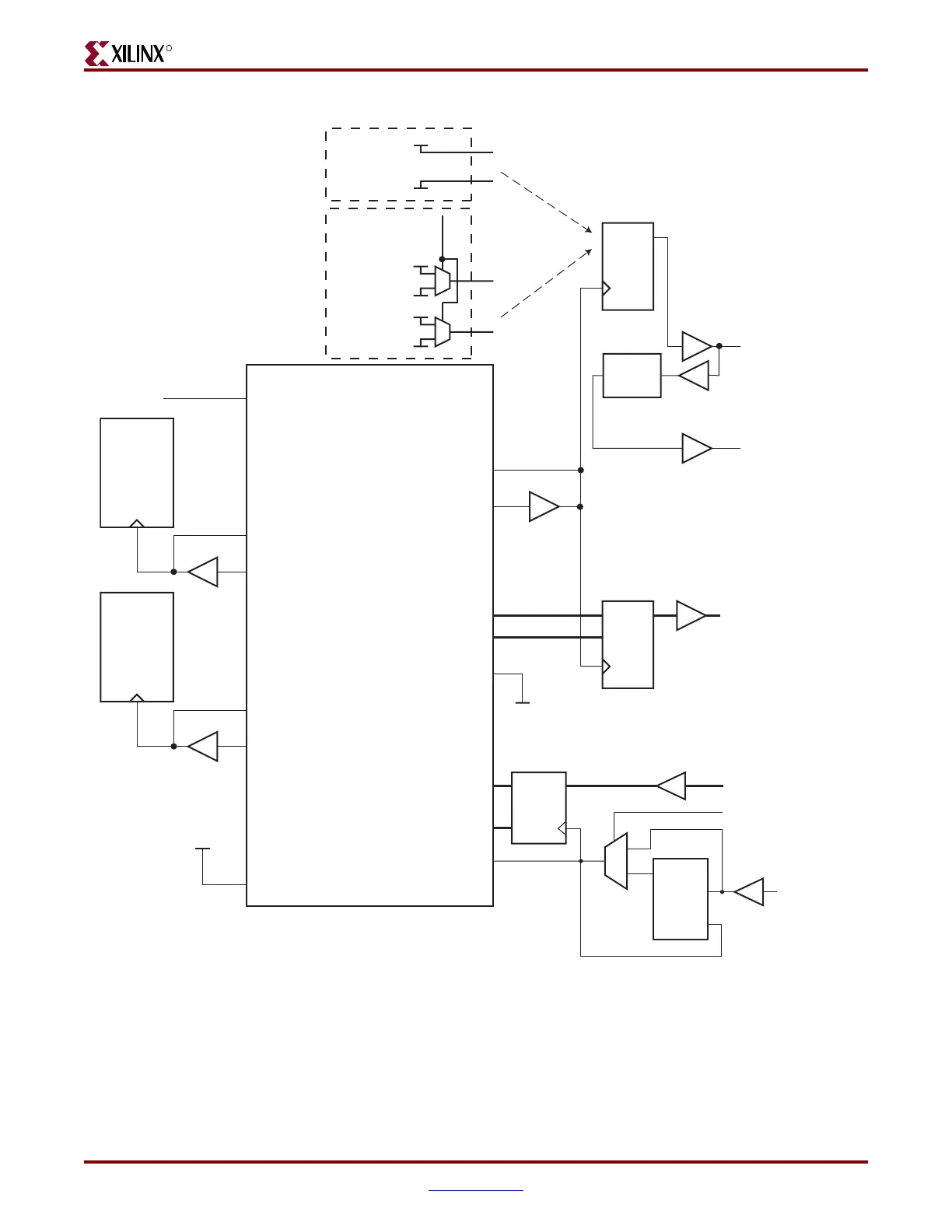

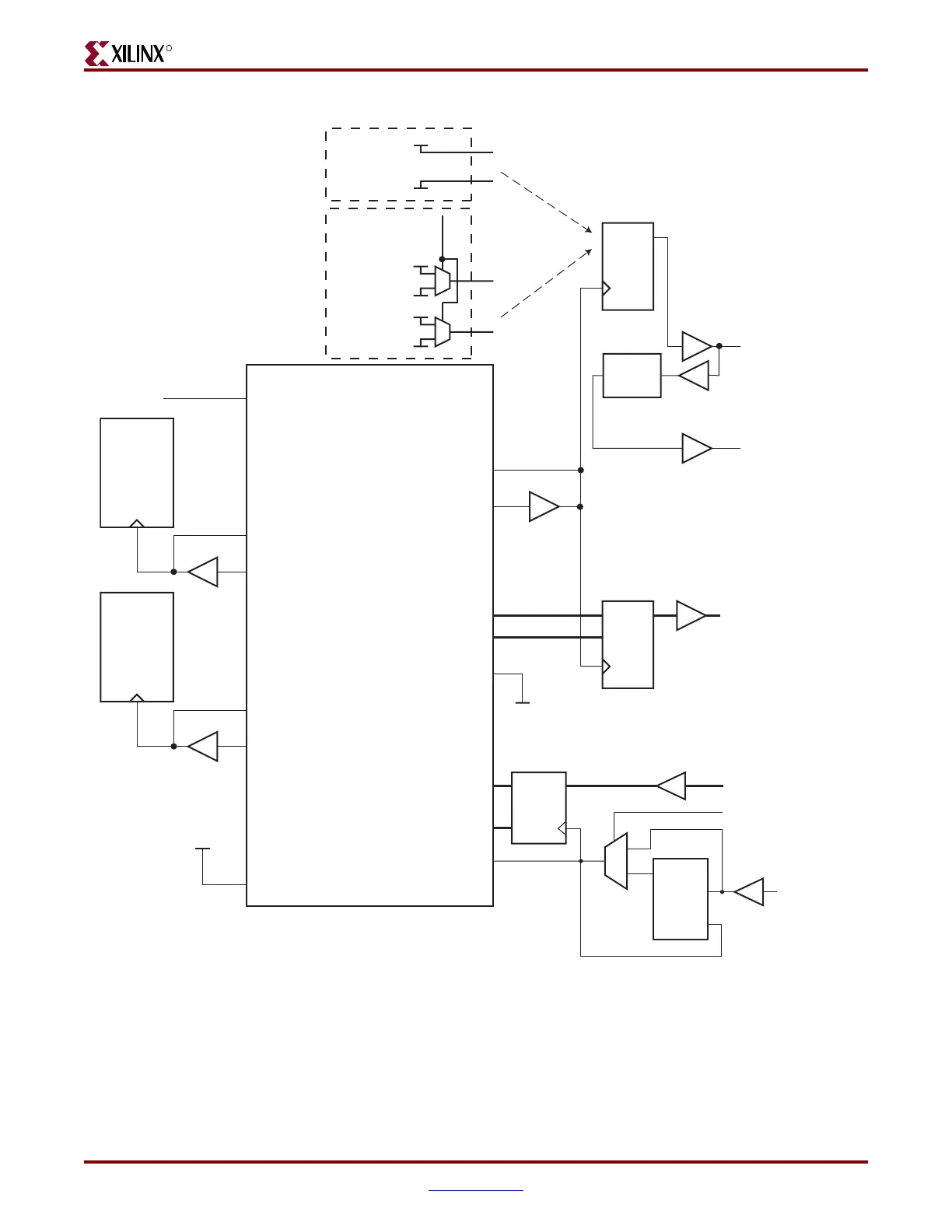

10/100/1000 RGMII

R

The CLIENTEMAC#DCMLOCKED port must be tied HIGH. The RGMII_RXC_# is

generated from the PHY and connected to the PHYEMAC#RXCLK pin and receive logic

through a DCM and a BUFG. A DCM must be used on the RGMII_RXC_# clock path as

illustrated in Figure 4-14 to meet the RGMII 1 ns setup and 1 ns hold requirements at

1 Gb/s. Phase shifting may then be applied to the DCM to fine-tune the setup and hold

Figure 4-15: Alternative Tri-Mode RGMII v2.0 Clock Management

EMAC#

PHYEMAC#GTXCLK

CLIENTEMAC#TXGMIIMIICLKIN

EMAC#CLIENTTXGMIIMIICLKOUT

CLIENTEMAC#TXCLIENTCLKIN

EMAC#CLIENTTXCLIENTCLKOUT

EMAC#PHYTXD[3:0]

EMAC#PHYTXD[7:4]

PHYEMAC#MIITXCLK

CLIENTEMAC#DCMLOCKED

CLIENTEMAC#RXCLIENTCLKIN

EMAC#CLIENTRXCLIENTCLKOUT

GTX_CLK

TX Client

Logic

RX Client

Logic

BUFG

BUFG

OBUF

IBUF

ODDR

D1

D2

Q

RGMII_TXD_#[3:0]

BUFG

(1)

IDELAY

RGMII_IOB_#

OBUF

RGMII_TXC_#

IOBUF

ODDR

D1

D2

Q

0

1

0

1

SPEED_IS_10_100

D1

D2

V

CC

V

CC

V

CC

GND

GND

GND

D1

D2

No Connection

PHYEMAC#RXCLK

PHYEMAC#RXD[3:0]

PHYEMAC#RXD[7:4]

RGMII_RXD_#[3:0]

Q1

Q2

D

Notes:

1) A regional buffer (BUFR) can replace this BUFG.

Refer to the Virtex-4 User Guide for BUFR usage guidelines.

UG074_3_79_031009

CLKIN

CLKFB

DCM

CLK0

SPEED_IS_10_100

BUFGMUX

RGMII_RXC_#

IBUFG

0

1

Loading...

Loading...