132 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 4: Physical Interface

R

To ensure that the Ethernet MAC does not operate until the MGT has achieved all

necessary locks, the CLIENTEMAC#DCMLOCKED input signal to the EMAC# block is

generated using the TXLOCK and RXLOCK signals from the MGT, and the DCM

LOCKED output. Refer to the CORE Generator Ethernet MAC wrapper for the actual

implementation of this combined lock signal.

The EMAC#CLIENTRXCLIENTCLKOUT output port must be connected to a BUFG to

drive the receive client logic in the FPGA fabric, and then is routed back into the input

ports CLIENTEMAC#RXCLIENTCLKIN and CLIENTEMAC#TXCLIENTCLKIN. This

clock is also used for the transmit client logic.

SGMII Signals

An Ethernet MAC wrapper has all necessary pin connections to configure the primitive

into SGMII. Table 4-6 describes the 10/100/1000 SGMII interface signals.

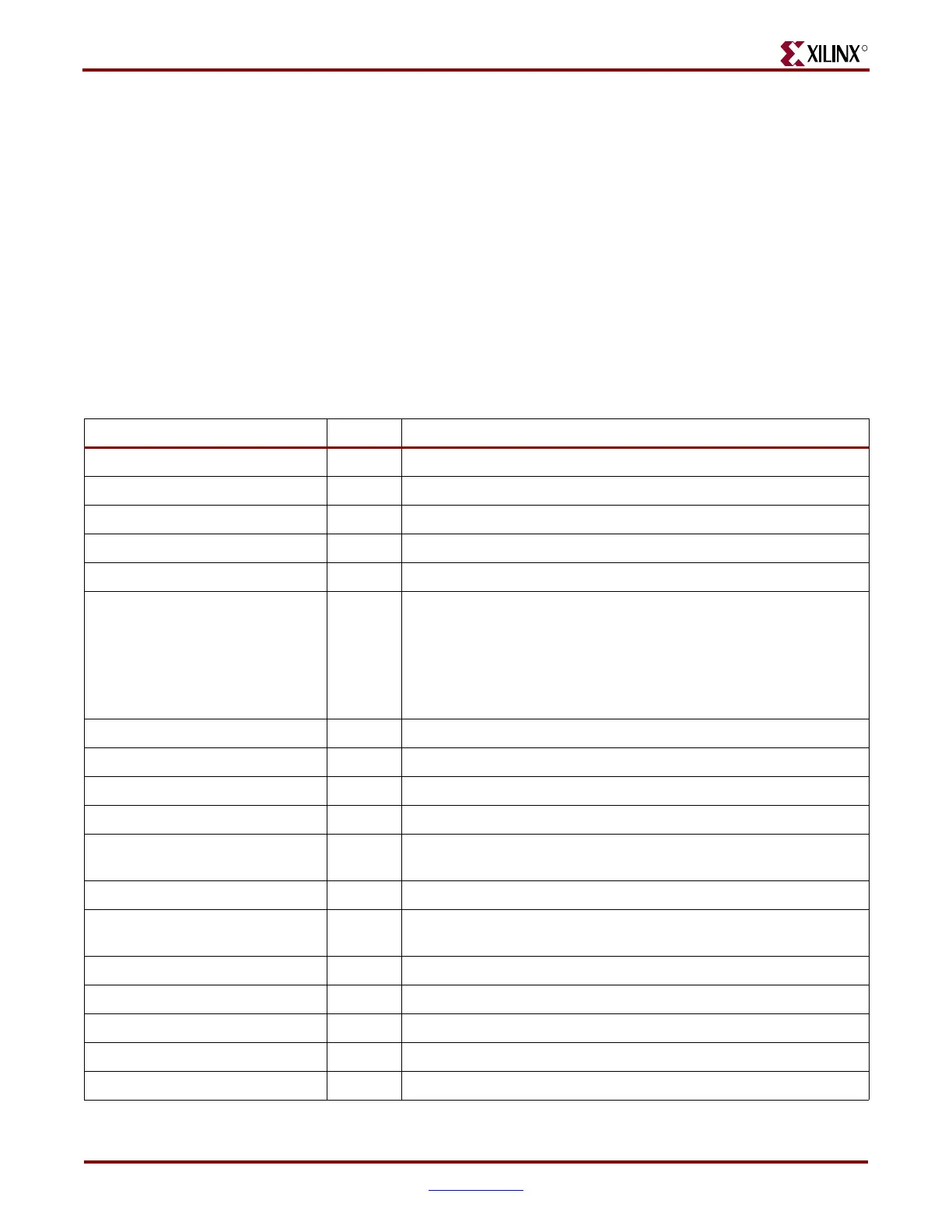

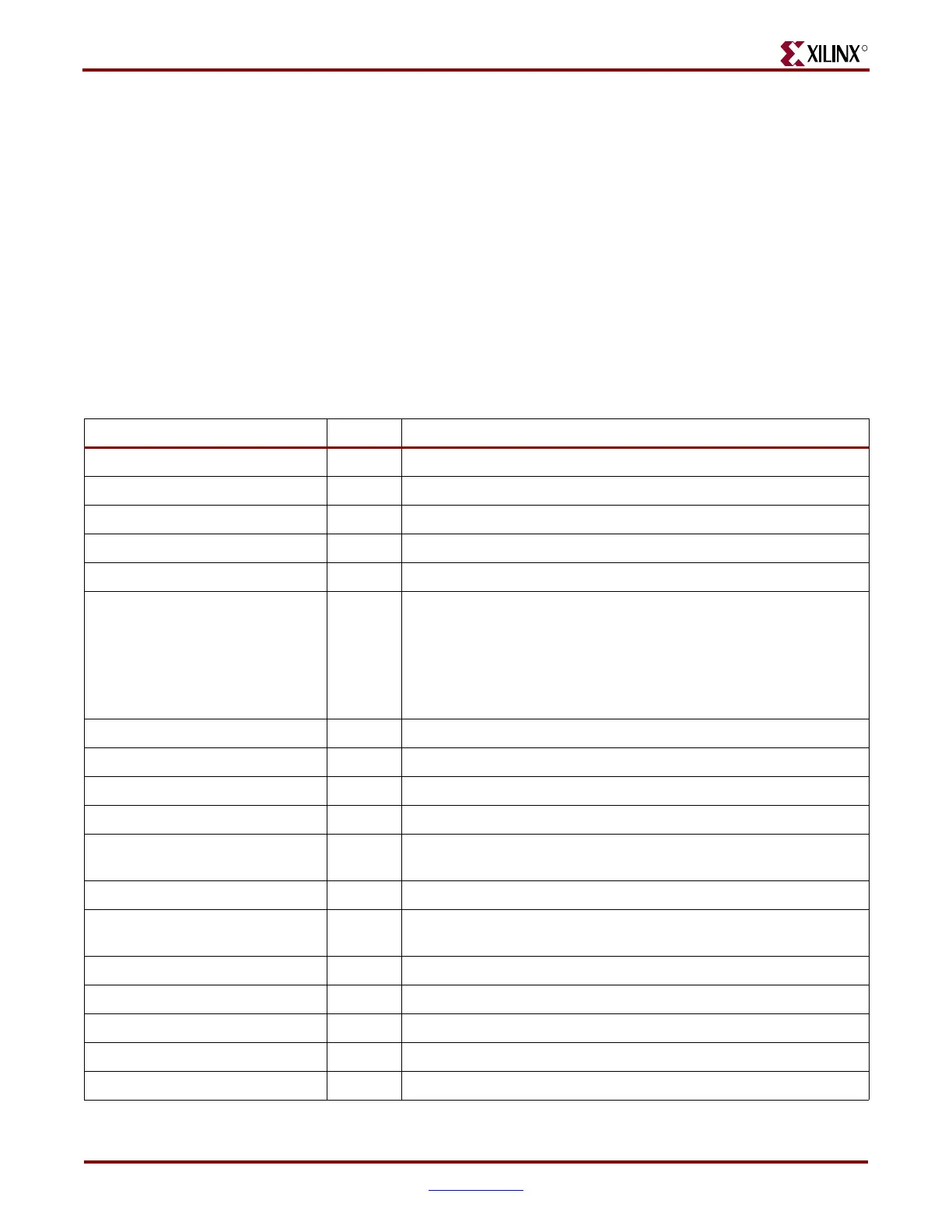

Table 4-6: 10/100/1000 SGMII and 1000BASE-X PCS/PMA Interface Signals

Signal Direction Description

ENCOMMAALIGN_# Output Enable PMA layer (MGT) to realign to commas.

LOOPBACKMSB_# Output Loopback tests within the MGTs.

MGTRXRESET_# Output Reset to receive PCS of MGT.

MGTTXRESET_# Output Reset to transmit PCS of MGT.

POWERDOWN_# Output Power down the MGTs.

SYNC_ACQ_STATUS_# Output

The output from the receiver’s synchronization state machine of IEEE

Std 802.3, Clause 36.

When asserted High, synchronization on the received bitstream is

obtained. The state machine is in one of the SYNC_AQUIRED states of

IEEE Std 802.3 Figure 36-9.

When deasserted Low, synchronization is not yet obtained.

TXCHARDISPMODE_# Output Set running disparity for current byte.

TXCHARDISPVAL_# Output Set running disparity value.

TXCHARISK_# Output K character transmitted in TXDATA.

PHYAD[4:0]_# Input PHY address of MDIO register set for the PCS sublayer.

RXBUFSTATUS[1:0]_# Input

Receiver elastic buffer status: Bit [1] asserted indicates over flow or

underflow.

RXCHARISCOMMA_# Input Comma detected in RXDATA.

RXCHARISK_# Input

K character received or extra data bit in RXDATA. Becomes the 10th bit

in RXDATA when RXNOTINTABLE is asserted.

RXCHECKINGCRC_# Input Reserved, tie to GND.

RXBUFERR_# Input Reserved, tie to GND.

RXCOMMADET_# Input Reserved, tie to GND.

RXDISPERR_# Input Disparity error in RXDATA.

RXLOSSOFSYNC[1:0]_# Input Reserved, tie to GND.

Loading...

Loading...