Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 91

UG074 (v2.2) February 22, 2010

Host Interface

R

The IRENABLE register (Address Code 0x3A4) in the host interface is used to enable

interrupt bits in the IRSTATUS register. To enable an interrupt, the corresponding bit is set.

When the enable bit is cleared, the interrupt status is not updated.

For examples of DCR read and write accesses, see “Interfacing to the Processor DCR” in

Chapter 6.

Address Code

The address codes for the Ethernet MAC registers are divided into three groups as shown

in Table 3-29. The unused address codes are reserved. The detailed address codes for each

register are described in Table 3-30. The address codes for the Ethernet MAC registers and

registers in the host interface are encoded in hardware. Address codes for statistics IP

registers and Ethernet MAC Configuration registers match the 1G Ethernet MAC Host Bus

address as specified in the Xilinx® 1G Ethernet MAC core at:

http://www.xilinx.com/support/documentation/ip_documentation/gig_eth_mac_ds200.pdf.

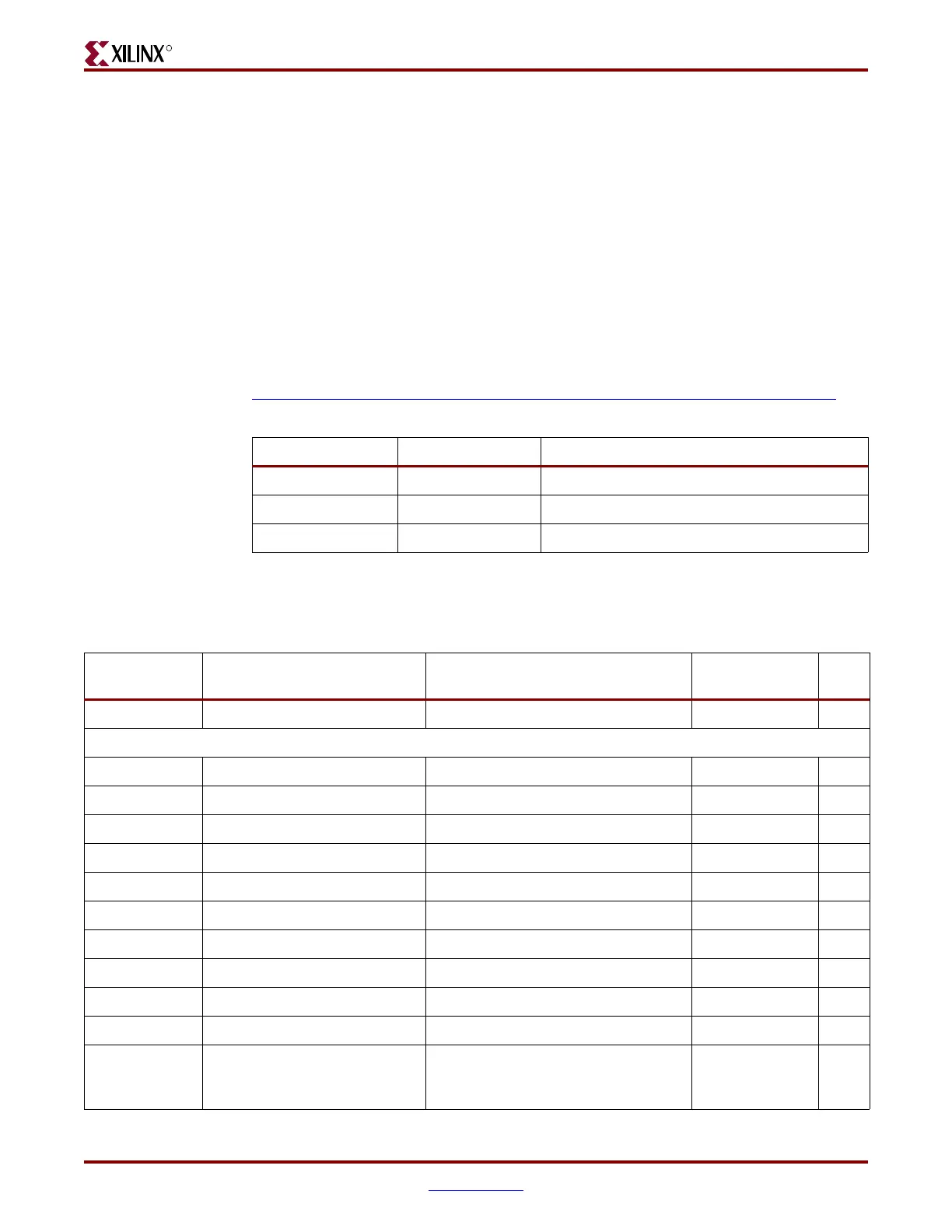

Table 3-29: Address Code Groups for DCR Host Bus Access

Group Address Code Description

EMAC0 0x200 – 0x39F EMAC0 registers.

Host Interface 0x3A0 – 0x3FF Host interface registers.

EMAC1 0x600 – 0x79F EMAC1 registers.

Notes:

1. Any access to the host interface registers does not generate interrupts and does not change the

RDYSTATUS register bits.

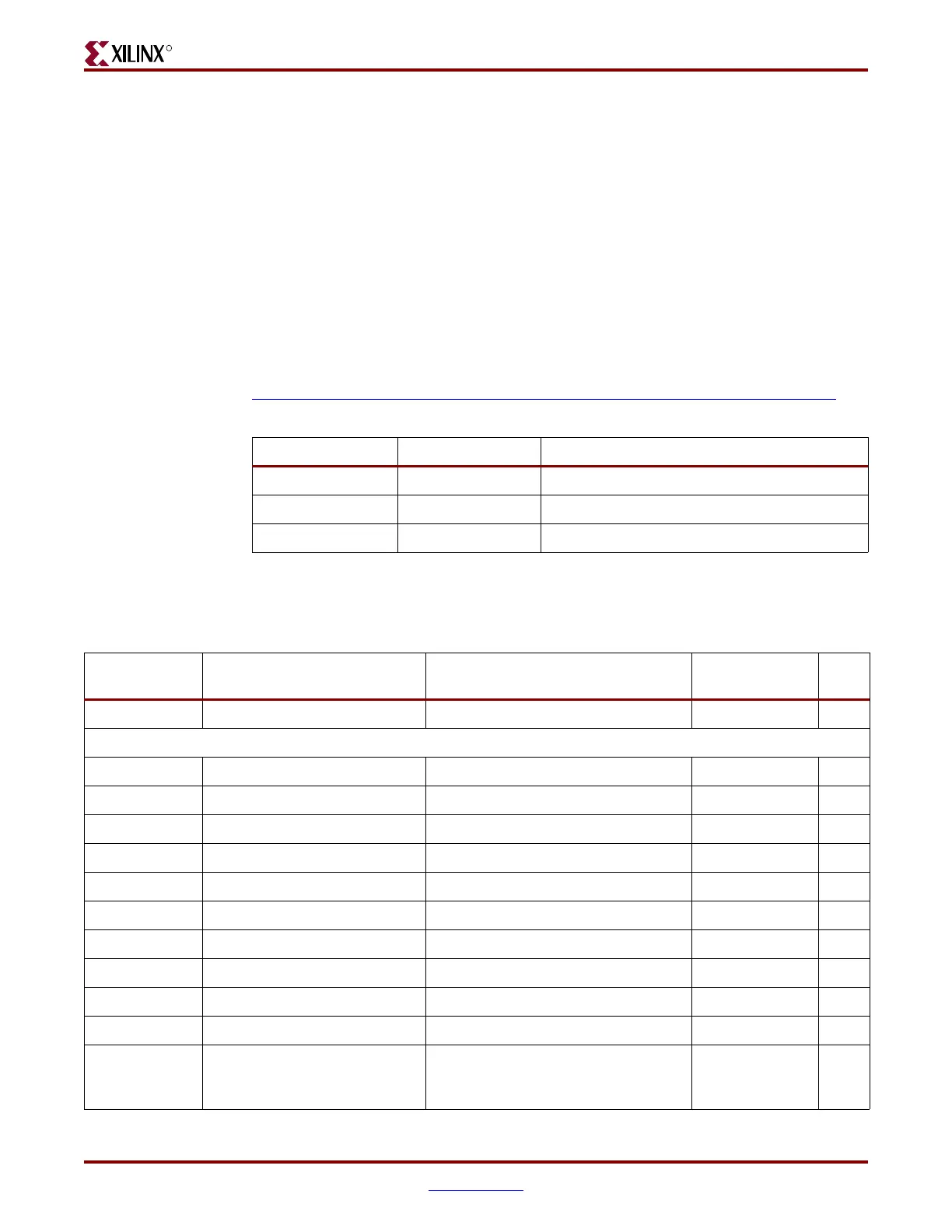

Table 3-30: Detailed Address Codes for DCR Host Bus Access

Address

Codes

Register Names Description

Ethernet MAC

Register Address

R/W

0x0:0x1FF Reserved.

EMAC0 Registers:

0x200 E0_RXCONFIGW0 Receiver configuration word 0. 0x200 R/W

0x240 E0_RXCONFIGW1 Receiver configuration word 1. 0x240 R/W

0x280 E0_TXCONFIG Transmitter configuration. 0x280 R/W

0x2C0 E0_FLOWCONTROL Flow control configuration. 0x2C0 R/W

0x300 E0_EMACCONFIG Ethernet MAC configuration. 0x300 R/W

0x320 E0_RGMII_SGMII RGMII/SGMII configuration. 0x320 R

0x340 E0_MGMTCONFIG Management configuration. 0x340 R/W

0x380 E0_UNICASTADDRW0 Unicast address [31:0]. 0x380 R/W

0x384 E0_UNICASTADDRW1 0x0000, unicast address [47:32]. 0x384 R/W

0x388 E0_ADDRTABLECONFIGW0 Multicast address data [31:0] 0x388 R/W

0x38C E0_ADDRTABLECONFIGW1

0x00, RNW,

00000, ADDR[1:0],

Multicast address data [47:32]

0x38C R/W

Loading...

Loading...