Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 135

UG074 (v2.2) February 22, 2010

1000BASE-X PCS/PMA

R

1000BASE-X PCS/PMA

The full-duplex PCS with PMA interface for 1000BASE-X is defined in IEEE Std 802.3-2002,

Clauses 36 and 37.

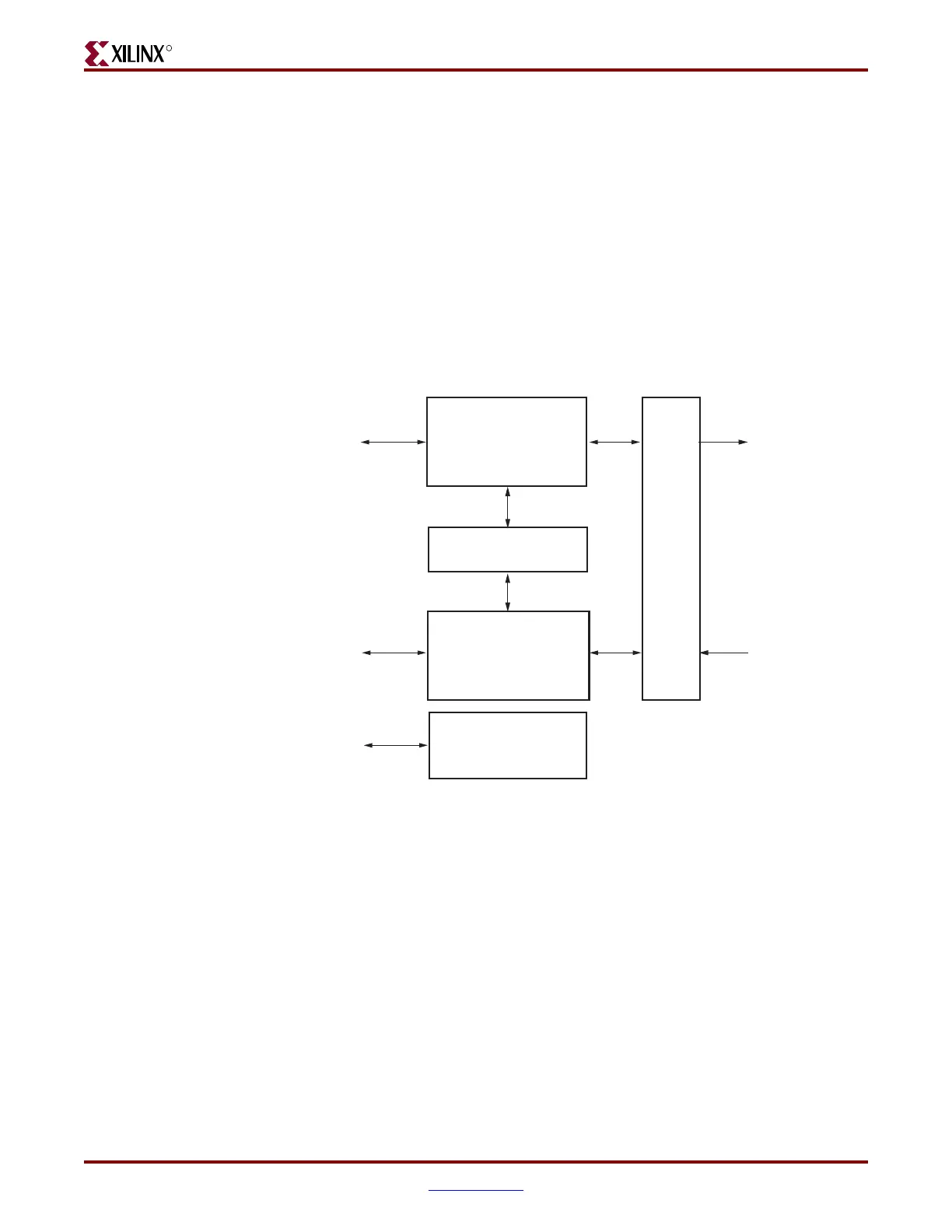

Figure 4-25 shows a block diagram of the PCS and PMA sublayers. The functional blocks

of the PCS and PMA sublayers can replace the GMII interface. The functional blocks of the

PCS and PMA sublayers are:

• Transmit engine

• Auto-negotiation block

• Receive engine and synchronization block

• PCS management register block

• RocketIO transceiver

The management register block in the PCS sublayer is accessed through the MDIO

interface as though there is an externally connected PHY. This block is used to configure

the operation of the PCS sublayer, the PMA sublayer, and auto-negotiation. The host

interface can control the MDIO interface as defined in “MDIO Interface” in Chapter 3.

When the management interface is not present, the PCS sublayer management register

block must be accessed using a separate MDIO controller outside the Ethernet MAC.

The MGT provides some of the PCS layer functionality including 8B/10B encoding and

decoding, and serialization and deserialization in the PMA layer.

1000BASE-X PCS/PMA Interface

Figure 4-26 shows the Ethernet MAC configured with 1000BASE-X PCS/PMA as the

physical interface. The client interfaces can be either 8 bits or 16 bits wide. In 16-bit client

mode, the Ethernet MAC can operate at 250 MHz, enabling a 2.5 Gb/s line rate. In this

interface, not all the ports of the Ethernet MAC are used.

Figure 4-25: Ethernet PCS/PMA Sublayer Extension

PCS Transmit

Engine

PCS Receive

Engine &

Synchronization

RocketIO Transceiver

PCS

Management

MDIO

Interface

Auto-negotiation

TXP/TXN

RXP/RXN

MAC TX

Interface

MAC RX

Interface

UG074_3_62_012508

Loading...

Loading...