Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 149

UG074 (v2.2) February 22, 2010

Ethernet MAC Configuration

R

PCS/PMA mode, EMAC#CLIENTTXGMIIMIICLKOUT is derived from the

PHYEMAC#GTXCLK. See Chapter 4, “Physical Interface” for clock usage.

Receive Clocking Scheme

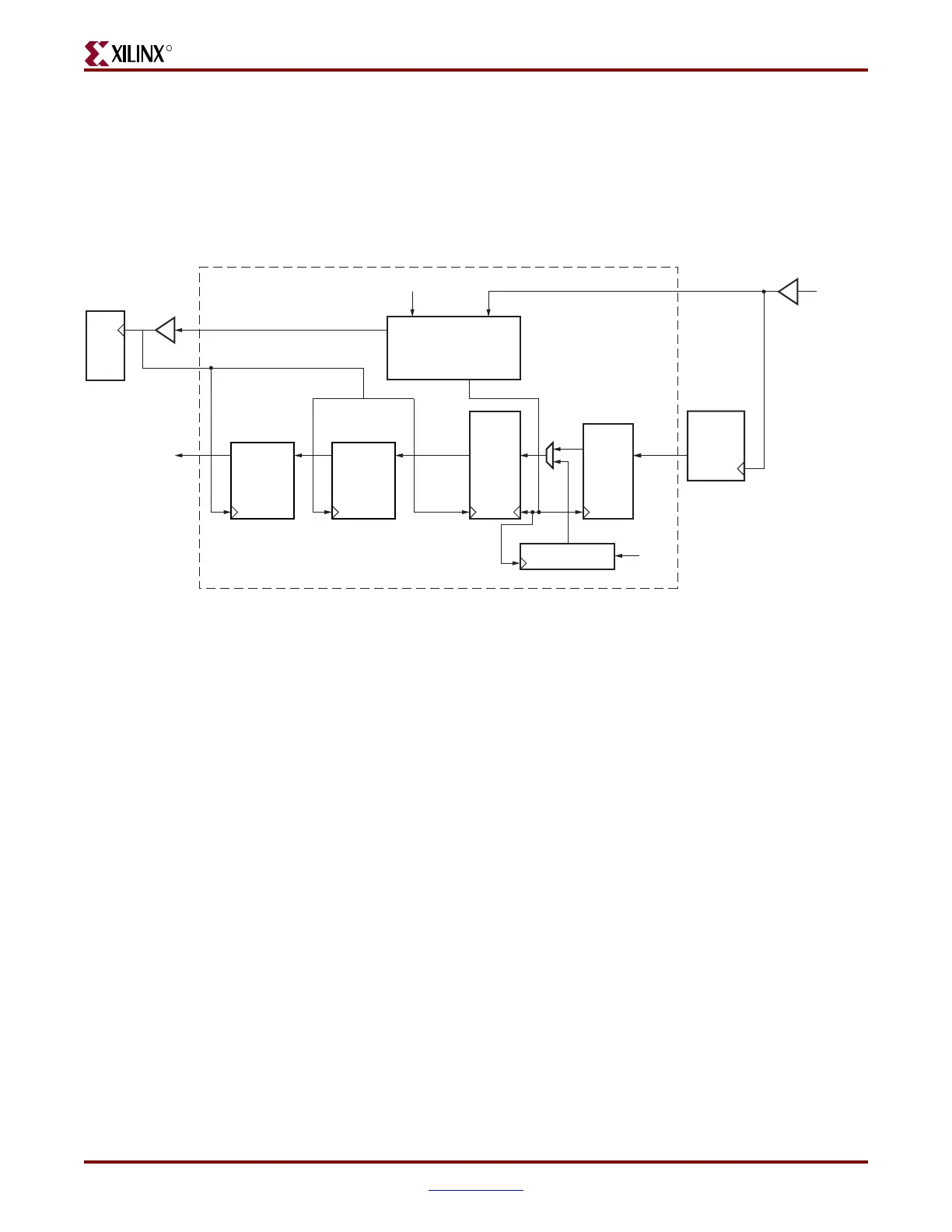

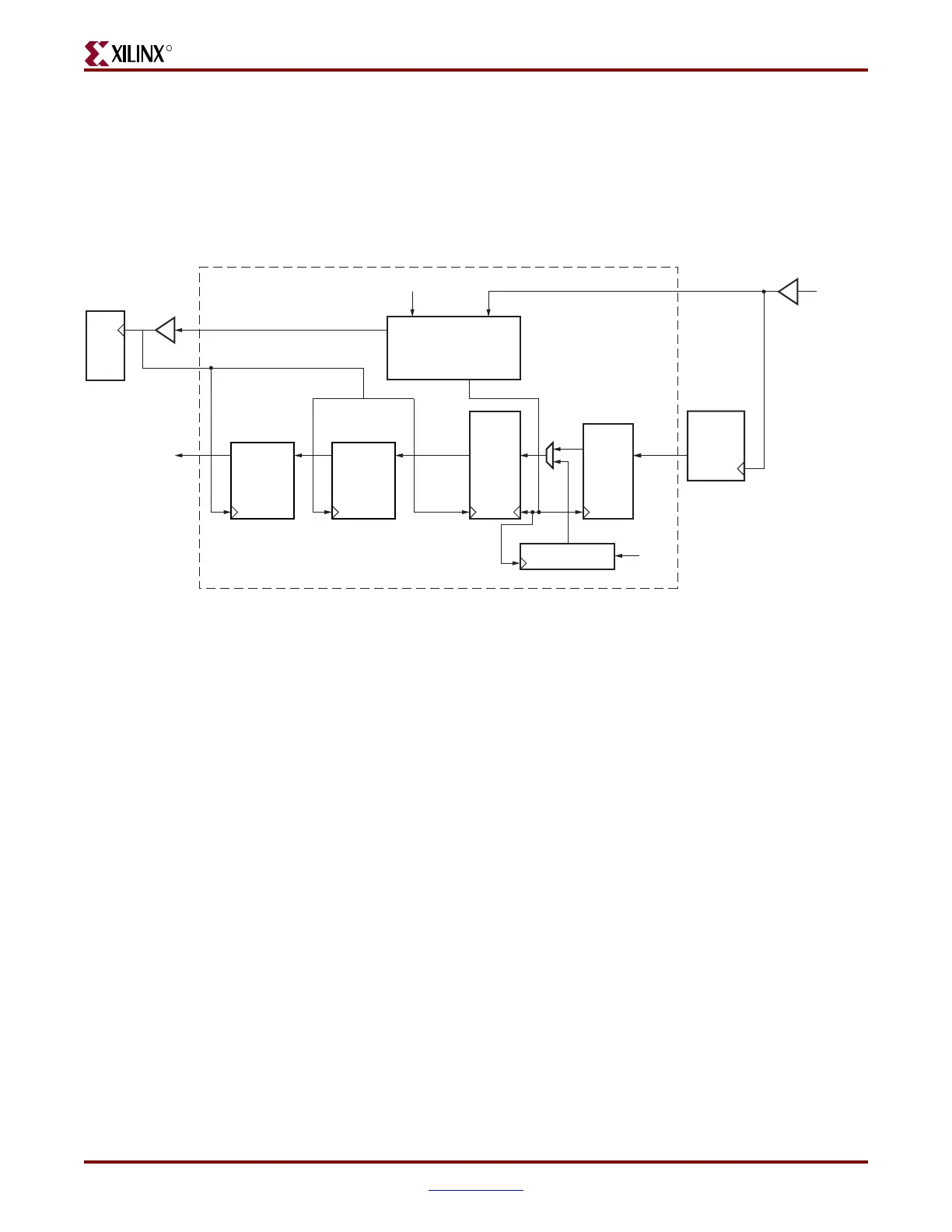

Figure 5-2 shows the clocks used in the receive module of the Ethernet MAC. In this figure,

RX_CORE_CLK and RX_GMII_MII_CLK are internal clock signals.

The clock generation module takes the PHYEMAC#RXCLK from the physical interface

and generates the EMAC#CLIENTRXCLIENTCLKOUT to run the circuitry in the FPGA

fabric connecting to the client side. CLIENTEMAC#RXCLIENTCLKIN runs the client logic

and receive engine inside the Ethernet MAC. This clock signal must be from the FPGA

clock drivers (BUFG) of EMAC#CLIENTRXCLIENTCLKOUT.

When configured in MII/GMII/RGMII mode, the internal RX_GMII_MII_CLK is derived

from the PHYEMAC#RXCLK and used to run the MII/GMII/RGMII sublayer. When the

Ethernet MAC is configured in either SGMII or 1000BASE-X PCS/PMA mode, the clock to

run the PCS/PMA sublayer is generated from the PHYEMAC#GTXCLK. See Chapter 4,

“Physical Interface” for clock usage.

Ethernet MAC Configuration

The Ethernet MAC can be configured using hardware or by accessing the registers through

the host interface in software. The three methods for configuration are described in the

following sections:

1. Tie-off pins in hardware (see “Tie-Off Pins” in Chapter 2)

2. Generic host bus using the host interface (see “Generic Host Bus” in Chapter 3)

3. DCR using the host interface (see “Using the DCR Bus as the Host Bus” in Chapter 3)

Table 5-6 shows the register addresses for each of the two Ethernet MACs.

Figure 5-2: Receive Clocks

CLKGEN

RX

Core

RX

Client

Datapath

Synchronous

Buffer

GMII/MII

PCS/PMA

RX_CORE_CLK

RX_GMII_MII_CLK

RXCLK

from PHY

EMAC#CLIENTRXCLIENTCLKOUT

PHYEMAC#RXCLKPHYEMAC#GTXCLK

CLIENTEMAC#RXCLIENTCLKIN

ug074_3_02_102004

GMII/MII

Logic

Client

Logic

BUFG

BUFG

Ethernet MAC Block

Loading...

Loading...