30 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 2: Ethernet MAC Architecture

R

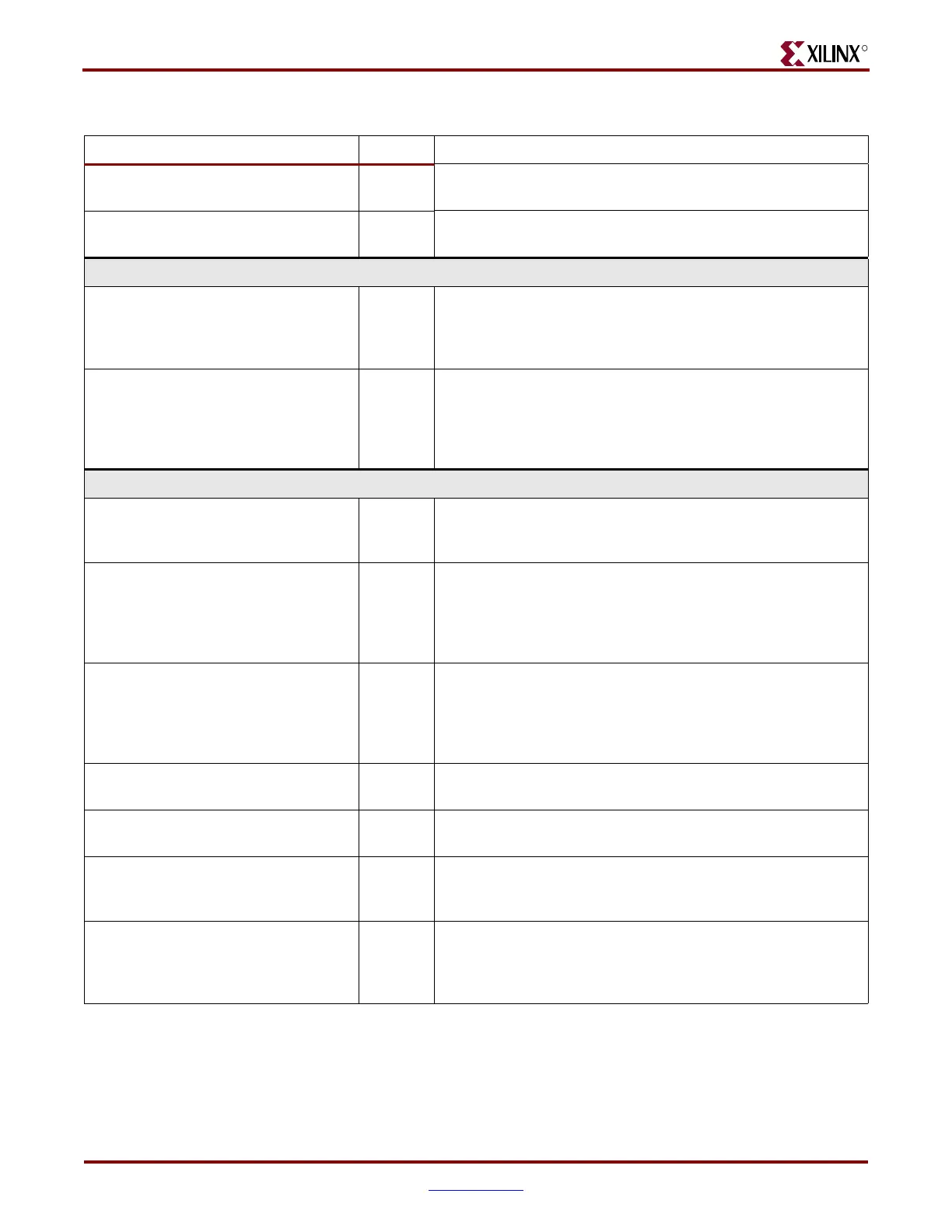

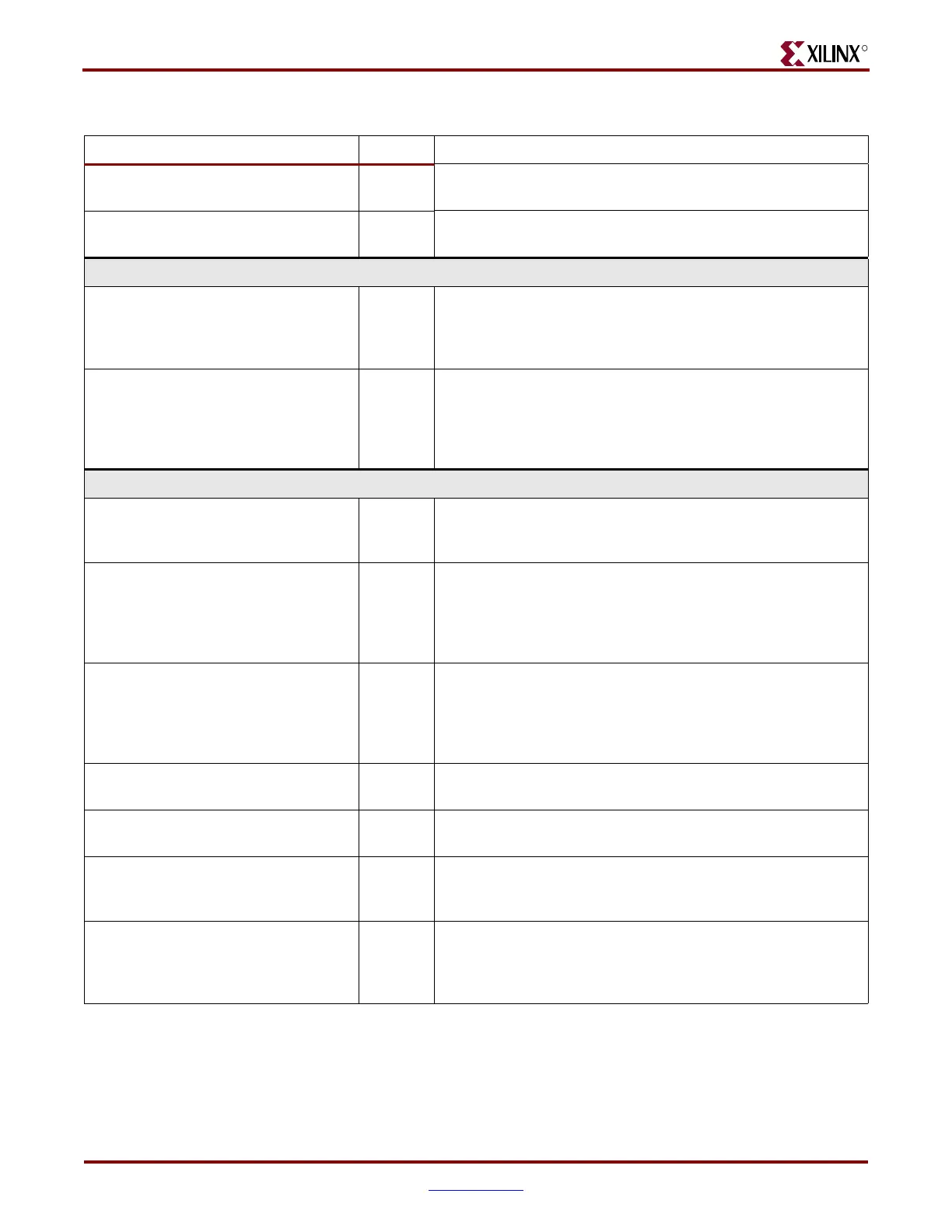

Table 2-11: MAC Configuration Pins

Signal Direction Description

TIEEMAC#CONFIGVEC[64] Input

Address Filter Enable: Asserting this pin enables the use of the

address filter module in the Ethernet MAC.

TIEEMAC#CONFIGVEC[63] Input

Length/Type Check Disable: When this pin is asserted, it

disables the comparison of the L/T field with the size of the data.

TIEEMAC#CONFIGVEC[62:61] — These pins configure the Ethernet MAC flow control module.

TIEEMAC#CONFIGVEC[62] Input

Receive Flow Control Enable. When this bit is

1 and full-duplex

mode is enabled,

the received flow control frames inhibit

transmitter operation. When this bit is 0, the received flow

frames are passed up to the client.

TIEEMAC#CONFIGVEC[61] Input

Transmit Flow Control Enable. When this bit is

1 and full duplex

mode is enabled,

asserting the CLIENTEMAC#PAUSE_REQ

signal causes the Ethernet MAC to send a flow control frame out

from the transmitter. When 0, asserting the

CLIENTEMAC#PAUSE_REQ signal has no effect.

TIEEMAC#CONFIGVEC[60:54] — Configures the transmit engine of the Ethernet MAC.

TIEEMAC#CONFIGVEC[60] Input

Transmitter Reset. When this bit is

1, the Ethernet MAC

transmitter is held in reset. This signal is an input to the reset

circuit for the transmitter block.

TIEEMAC#CONFIGVEC[59] Input

Transmitter Jumbo Frame Enable. When this bit is 1, the Ethernet

MAC transmitter allows frames larger than the maximum legal

frame length specified in IEEE Std 802.3-2002 to be sent. When

this bit is 0, the Ethernet MAC transmitter only allows frames up

to the legal maximum to be sent.

TIEEMAC#CONFIGVEC[58] Input

Transmitter In-Band FCS Enable. When this bit is

1, the Ethernet

MAC transmitter expects the FCS field to be passed in by the

client. When this bit is 0, the Ethernet MAC transmitter appends

padding as required, computes the FCS, and appends it to the

frame.

TIEEMAC#CONFIGVEC[57] Input

Transmitter Enable. When this bit is

1, the transmitter is

operational. When this bit is 0, the transmitter is disabled.

TIEEMAC#CONFIGVEC[56] Input

Transmitter VLAN Enable. When this bit is

1, the transmitter

allows the transmission of VLAN tagged frames.

TIEEMAC#CONFIGVEC[55] Input

Transmitter Half Duplex. When this bit is

1, the transmitter

operates in half-duplex mode. When this bit is 0, the transmitter

operates in full-duplex mode.

TIEEMAC#CONFIGVEC[54] Input

Transmitter IFG Adjust enable. When this bit is

1, the transmitter

reads the value of the CLIENTEMAC#TXIFGDELAY[7:0] port

and sets the IFG accordingly. When this bit is 0, the transmitter

always inserts at least the legal minimum IFG.

Loading...

Loading...