Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 85

UG074 (v2.2) February 22, 2010

Host Interface

R

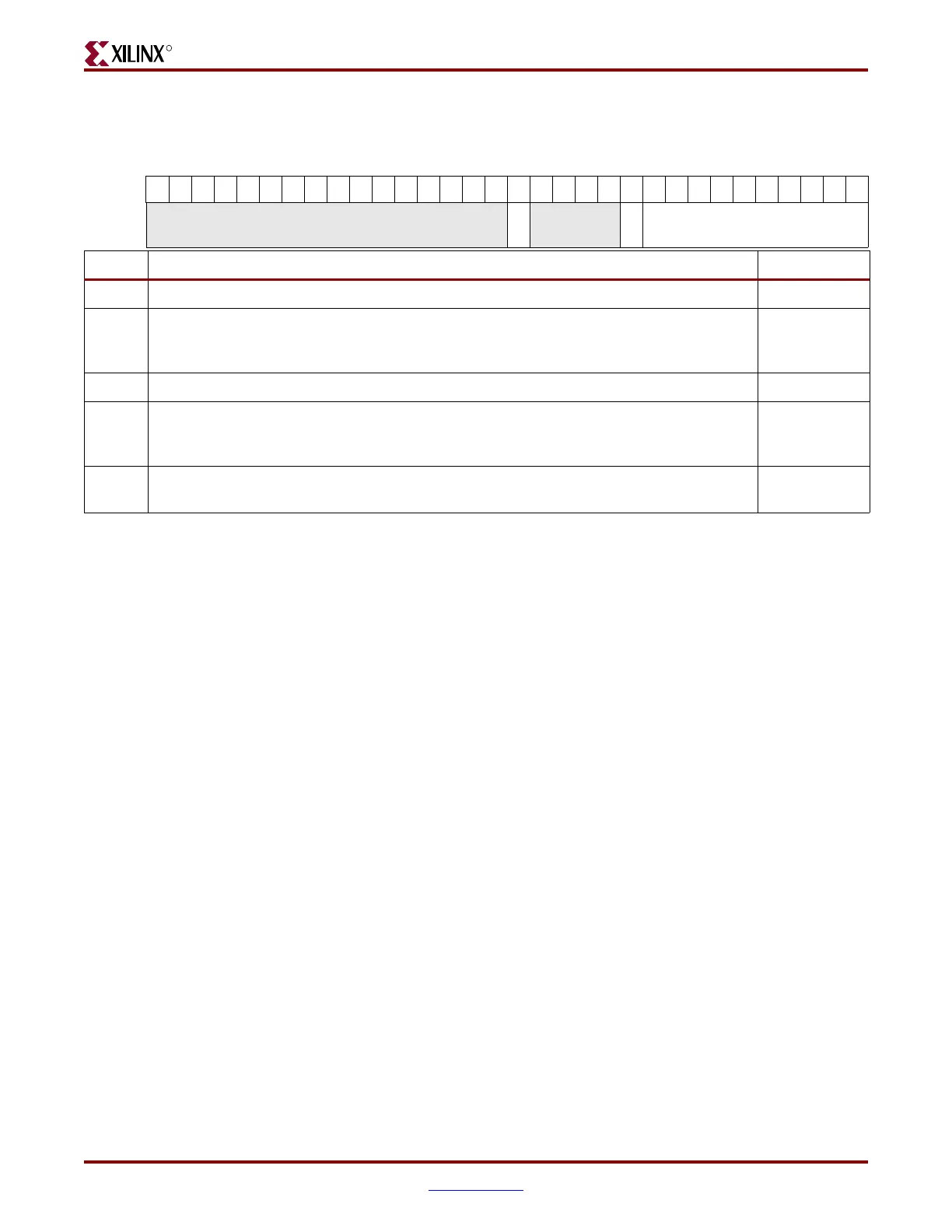

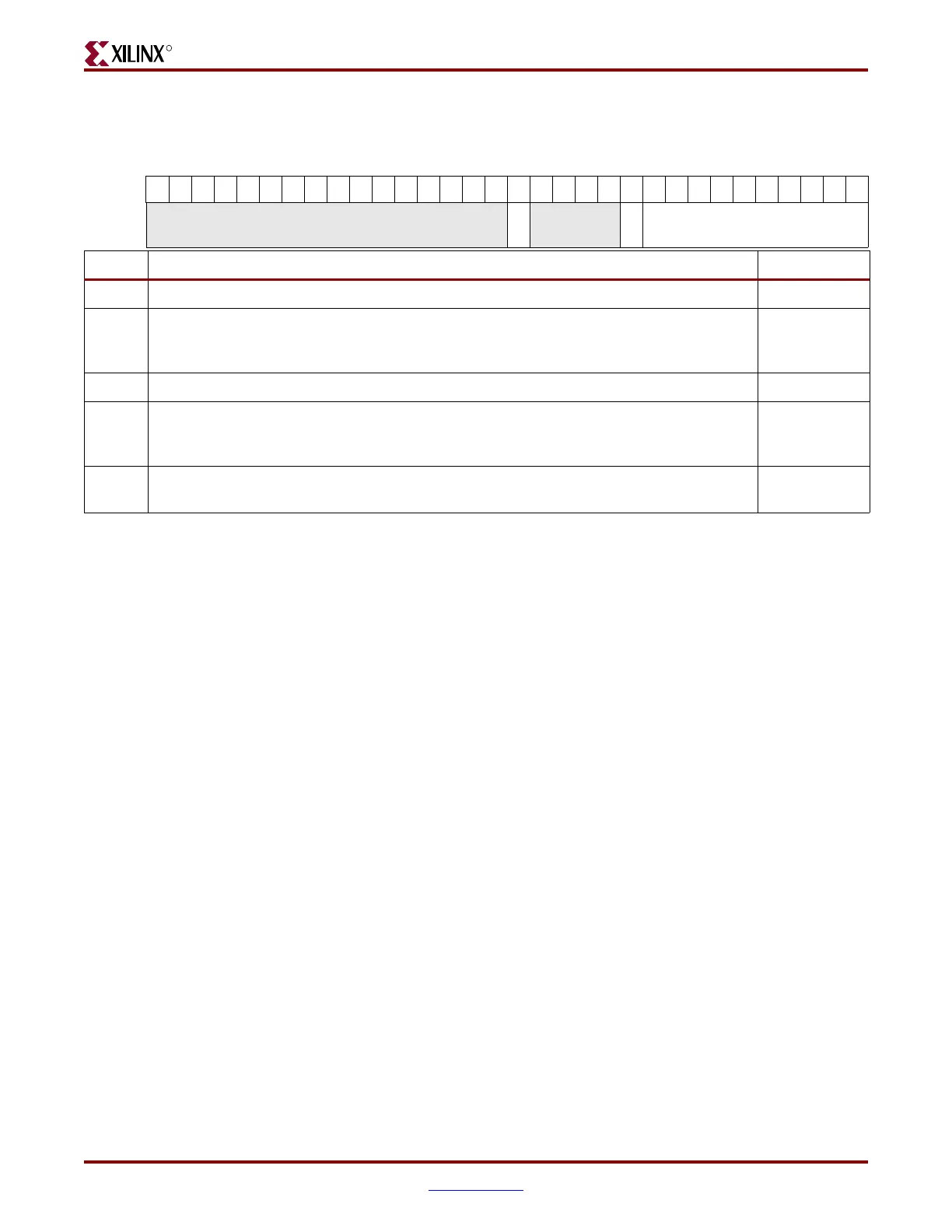

Table 3-24: DCR Control Register cntlReg

DCR

Offset

MSB

LSB

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

0xE

RESERVED

WEN

RESERVED

EMAC1

ADDRESS_CODE

Bit Description Default Value

[0:15] Reserved. All 0s

[16]

Write Enable – When this bit is asserted, the data in either dataRegLSW or dataRegMSW is

written into an Ethernet MAC register. When this bit is deasserted, the operation to be

performed is read.

0

[17:20] Reserved. All 0s

[21]

EMAC1SEL – When this bit is asserted, the address code is for the EMAC1 registers.

Otherwise, the address code is for the EMAC0 registers. This bit is essentially the bit [10] of

the address code.

0

[22:31]

Address Code – the DCR bus bridge translates this address code into the Ethernet MAC

register address. See Table 3-30, page 91 for address code.

All 0s

Loading...

Loading...