88 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 3: Client, Host, and MDIO Interfaces

R

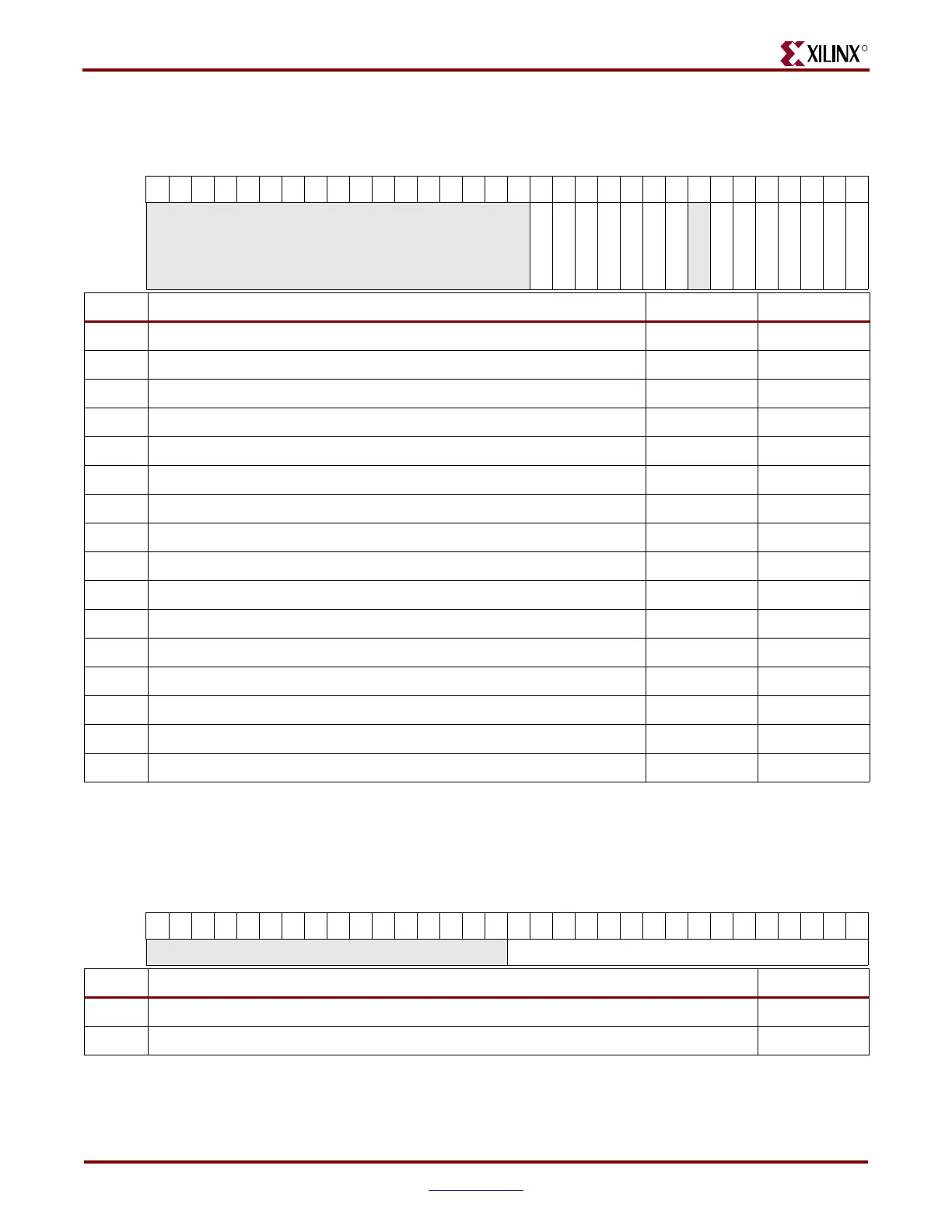

Table 3-27: Interrupt Enable Register IRENABLE

Address

Code

MSB

LSB

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

0x3A4

RESERVED

CFG WEN1

CFG REN1

AF WEN1

AF REN1

MIIM WEN1

MIIM REN1

STAT REN1

RSVD

CFG WEN0

CFG REN0

AF WEN0

AF REN0

MIIM WEN0

MIIM REN0

STAT REN0

Bit Description Ethernet MAC Default Value

[0:16] Reserved. – 0

[17] Configuration Write IR-enable bit. EMAC1 0

[18] Configuration Read IR-enable bit. EMAC1 0

[19] Address Filter Write IR-enable bit. EMAC1 0

[20] Address Filter Read IR-enable bit. EMAC1 0

[21] MDIO Write IR-enable bit. EMAC1 0

[22] MDIO Read IR-enable bit. EMAC1 0

[23] Statistics IP Read IR-enable bit.

(1)

EMAC1 0

[24] Reserved – 0

[25] Configuration Write IR-enable bit. EMAC0 0

[26] Configuration Read IR-enable bit. EMAC0 0

[27] Address Filter Write IR-enable bit. EMAC0 0

[28] Address Filter Read IR-enable bit. EMAC0 0

[29] MDIO Write IR-enable bit. EMAC0 0

[30] MDIO Read IR-enable bit. EMAC0 0

[31] Statistics IP Read IR enable bit.

(1)

EMAC0 0

Notes:

1. For more information on Statistics IP, see “Interfacing to an FPGA Fabric-Based Statistics Block” in Chapter 6.

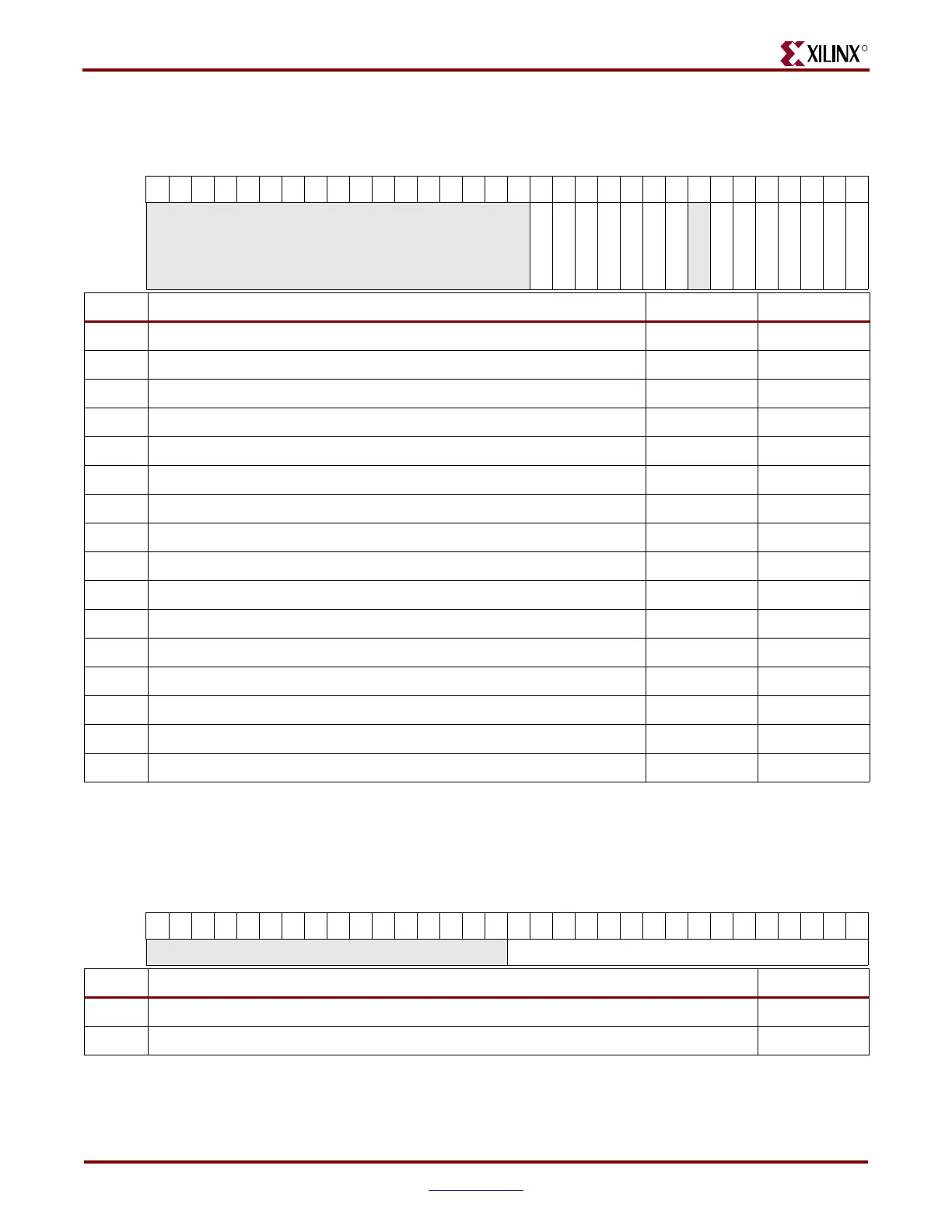

Table 3-28: Host Interface MDIO Write Data Register (MIIMWRDATA)

Address

Code

MSB

LSB

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

0x3B0

RESERVED MIIMWRDATA

Bit Description Default Value

[0:15] Reserved. All 0s

[16:31] Data- temporarily holds MDIO write data for output onto the host write data bus. undefined

Notes:

1. See “Interfacing to an FPGA Fabric-Based Statistics Block” in Chapter 6.

Loading...

Loading...