3-218

Performance Tests

ETSI/ANSI Internal Transmitter Clock Rates (Option 110)

ETSI/ANSI Internal Transmitter Clock Rates

(Option 110)

Specification

Description

A frequency Counter terminated in 75 ohms and connected to the Option 110 Trans-

mit Module front panel Clock Out Port is used to verify the frequency accuracy of

the transmitted data at all rates.

E3 (34.368Mb/s) Frequency Accuracy

1. Recall the HP 37717C Default Settings as shown on 3-2. Select TRANSMIT,

PDH/DSn, MAIN SETTINGS and set the SIGNAL to 34 Mb/s.

2. Adjust the Frequency Counter ATTEN and Trigger Level to obtain a stable

reading and ensure that the frequency counter reading is between 34367845.3 Hz and

34368154.7 Hz.

3. Set the FREQUENCY OFFSET to [USER OFFSET] [+20PPM].

4. Adjust the Frequency Counter ATTEN and Trigger Level to obtain a stable

reading and ensure that the frequency counter reading is between 34368532.7 Hz and

34368842.0 Hz.

5. Set the FREQUENCY OFFSET to [USER OFFSET] [-20PPM].

6. Adjust the Frequency Counter ATTEN and Trigger Level to obtain a stable

reading and ensure that the frequency counter reading is between 34367158.0 Hz and

34367467.3 Hz.

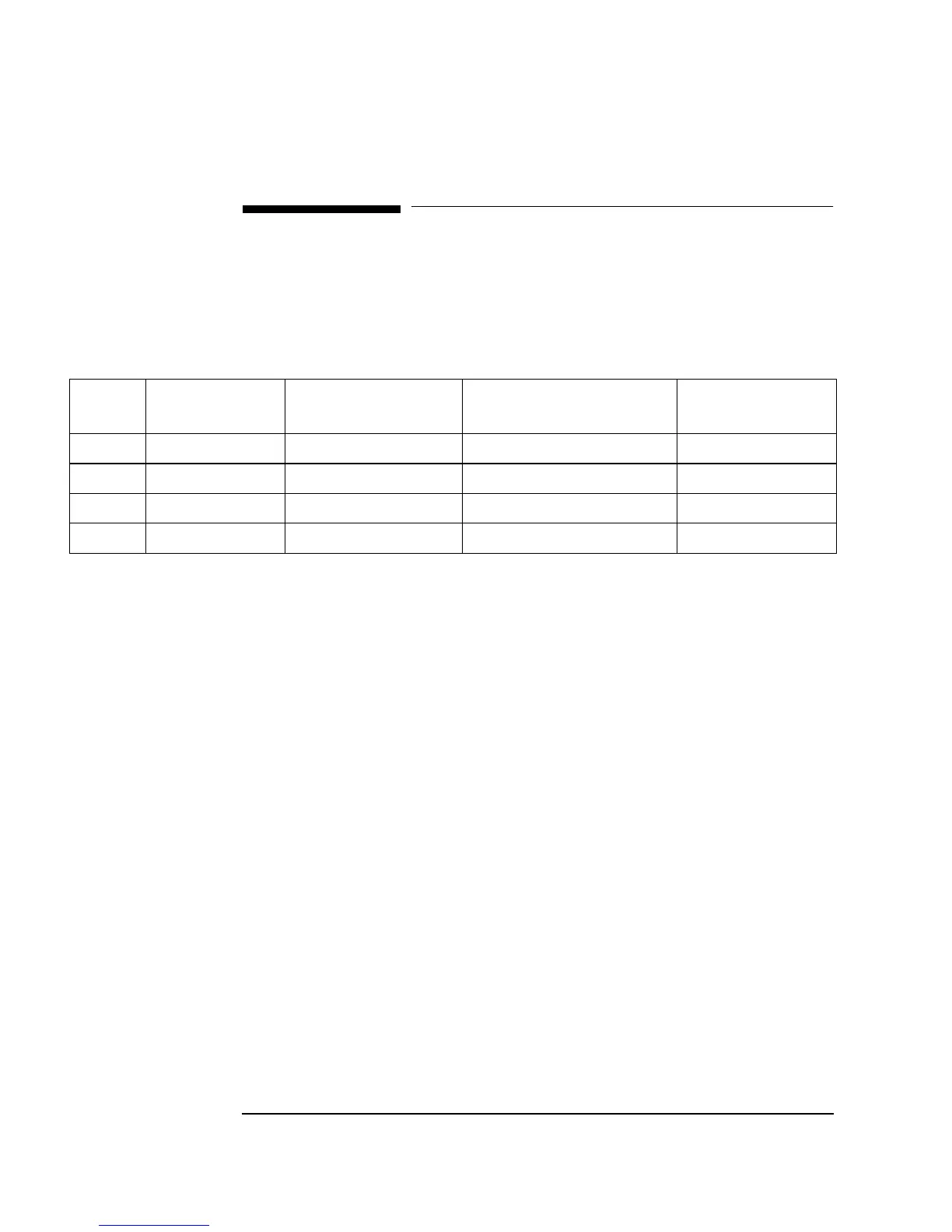

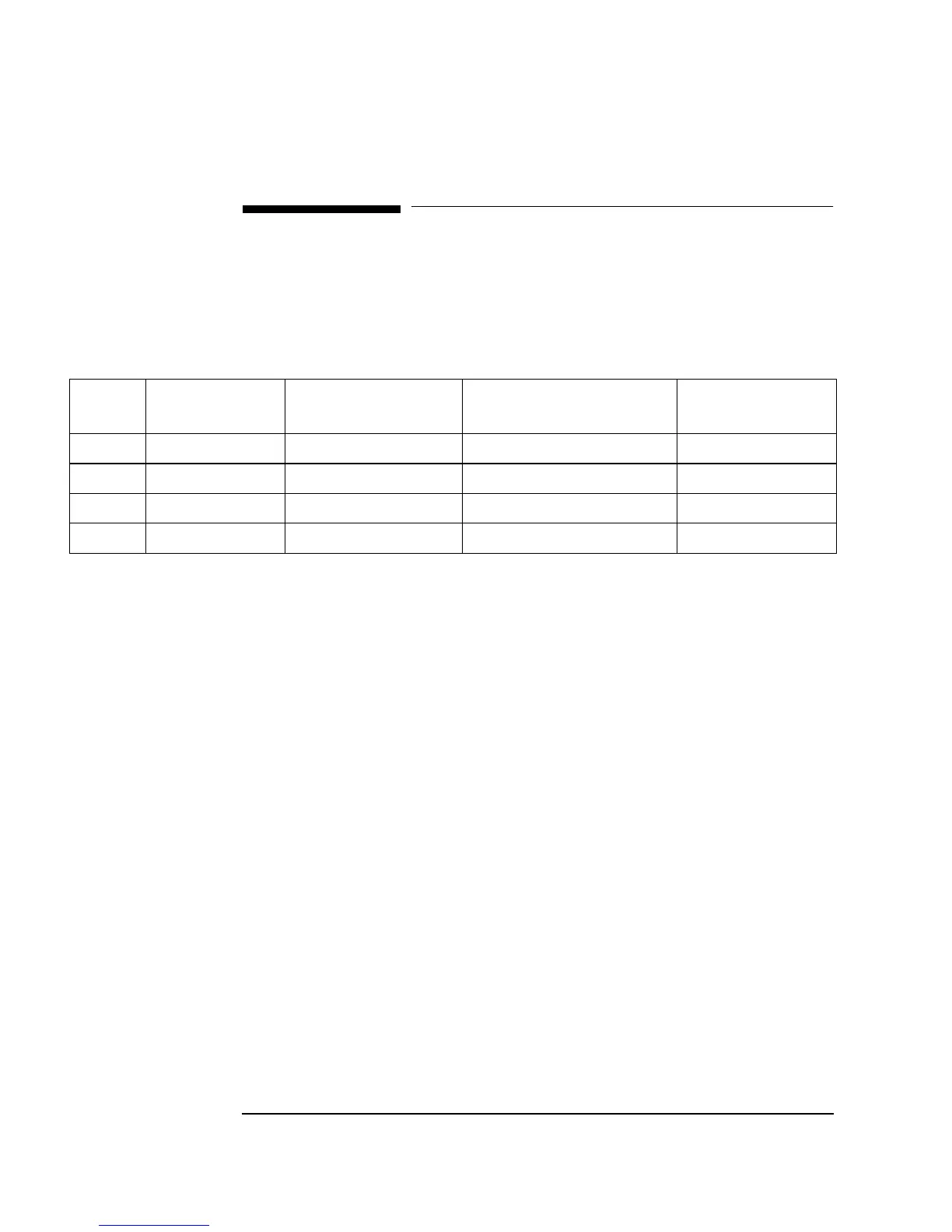

Rate Frequency Accuracy Temperature

Stability

Ageing

Stability

DS1 1.544Mb/s +/-0.7ppm @25C <=3ppm (0 to +50C) <=1ppm/Year

DS3 44.736Mb/s +/-0.5ppm @25C <=3ppm (0 to +50C) <=1ppm/Year

E1 2.048Mb/s +/-0.5ppm @25C <=3ppm (0 to +50C) <=1ppm/Year

E3 34.368Mb/s +/-0.5ppm @25C <=3ppm (0 to +50C) <=1ppm/Year

Loading...

Loading...