6-43

BUS INTERFACE UNIT

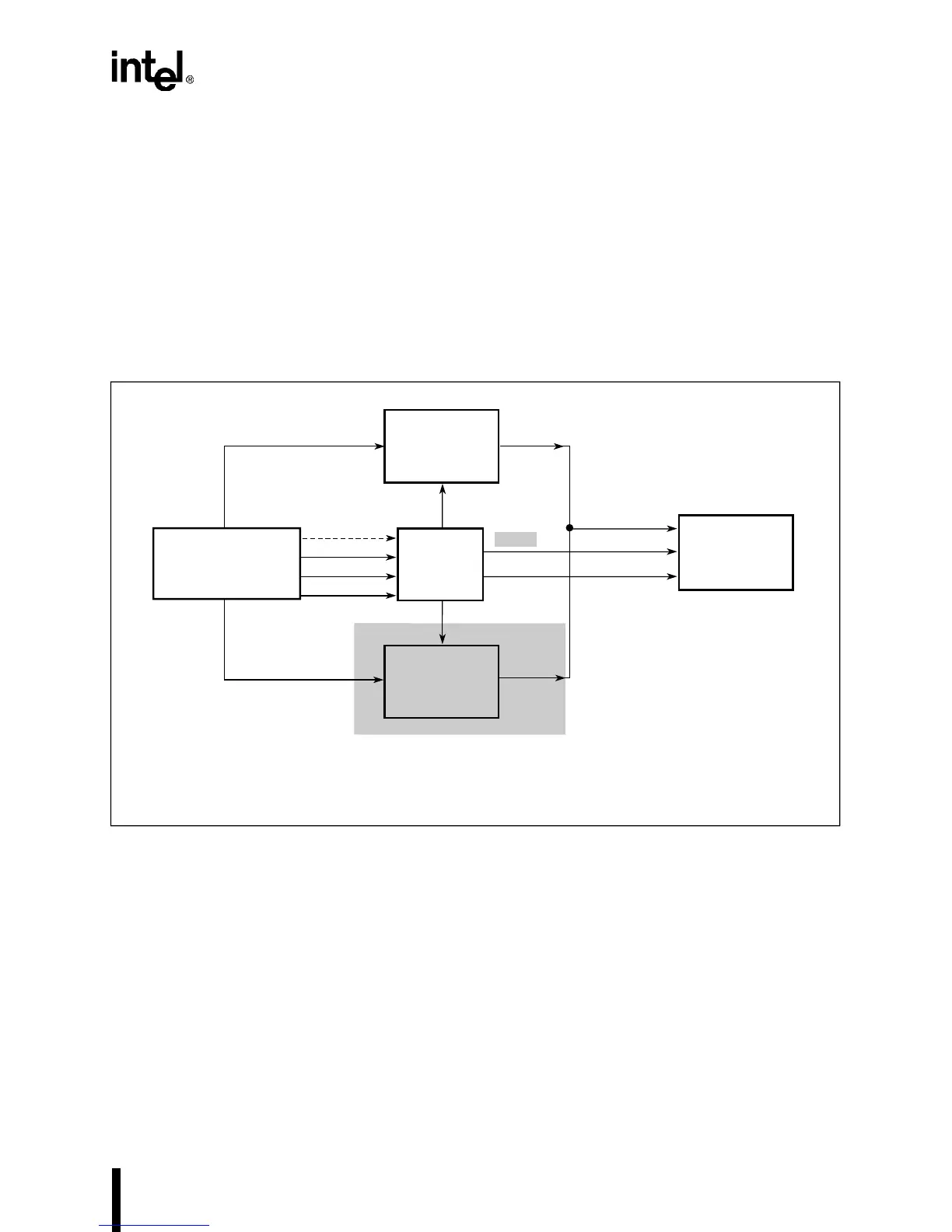

6.6.4 Paged DRAM Interface

External logic is required to interface the Intel386 EX processor to DRAM devices, as shown in

Figure 6-18. The PLD generates the RAS# and CAS# signals.

If RAS#-Only Refresh is being performed (using the Refresh Control Unit of the processor), then

during a Refresh Cycle, the PLD enables the Column Address Buffer and asserts the RAS# signal

(shaded sections in the figure). Refer to Chapter 6, “BUS INTERFACE UNIT,” for more infor-

mation.

A single multiplexer can be used instead of the separate row and column address buffers.

Figure 6-18. Intel386 EX Processor to Paged DRAM Interface

Intel386™ EX

Embedded Processor

Row

Address

Buffer

PLD

Upper Address

Row

Address

Paged

DRAM

Column

Address

Address

Lower Address

OE_ROW#

OE_COL#

RAS#

CAS#

BHE#

BLE#

A3264-02

Column

Address

Buffer

CS

n

#

REFRESH#

Note:

A single mux can be used in place of the row and column address buffers.

Loading...

Loading...