B-3

COMPATIBILITY WITH THE PC/AT* ARCHITECTURE

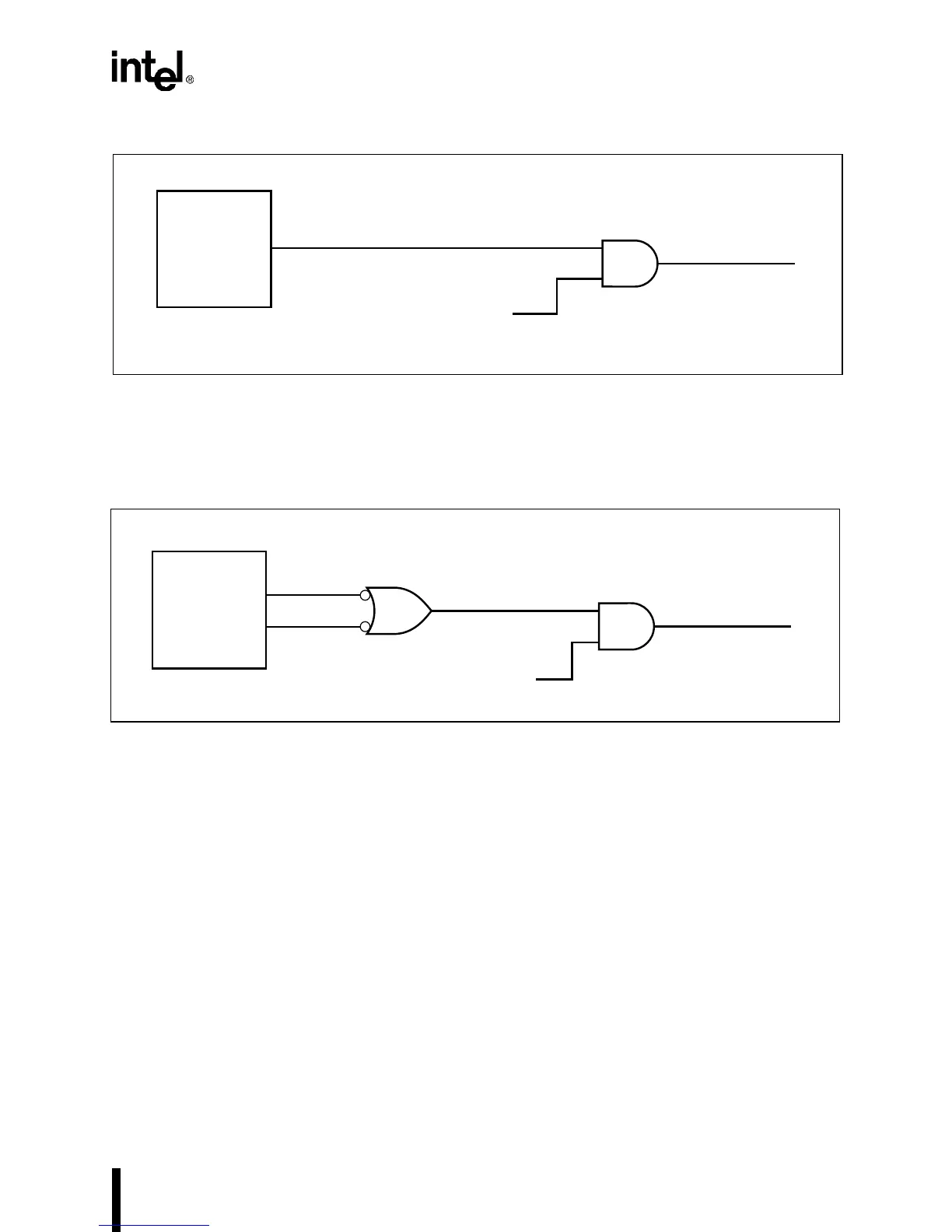

Figure B-1. Derivation of AEN Signal in a Typical PC/AT System

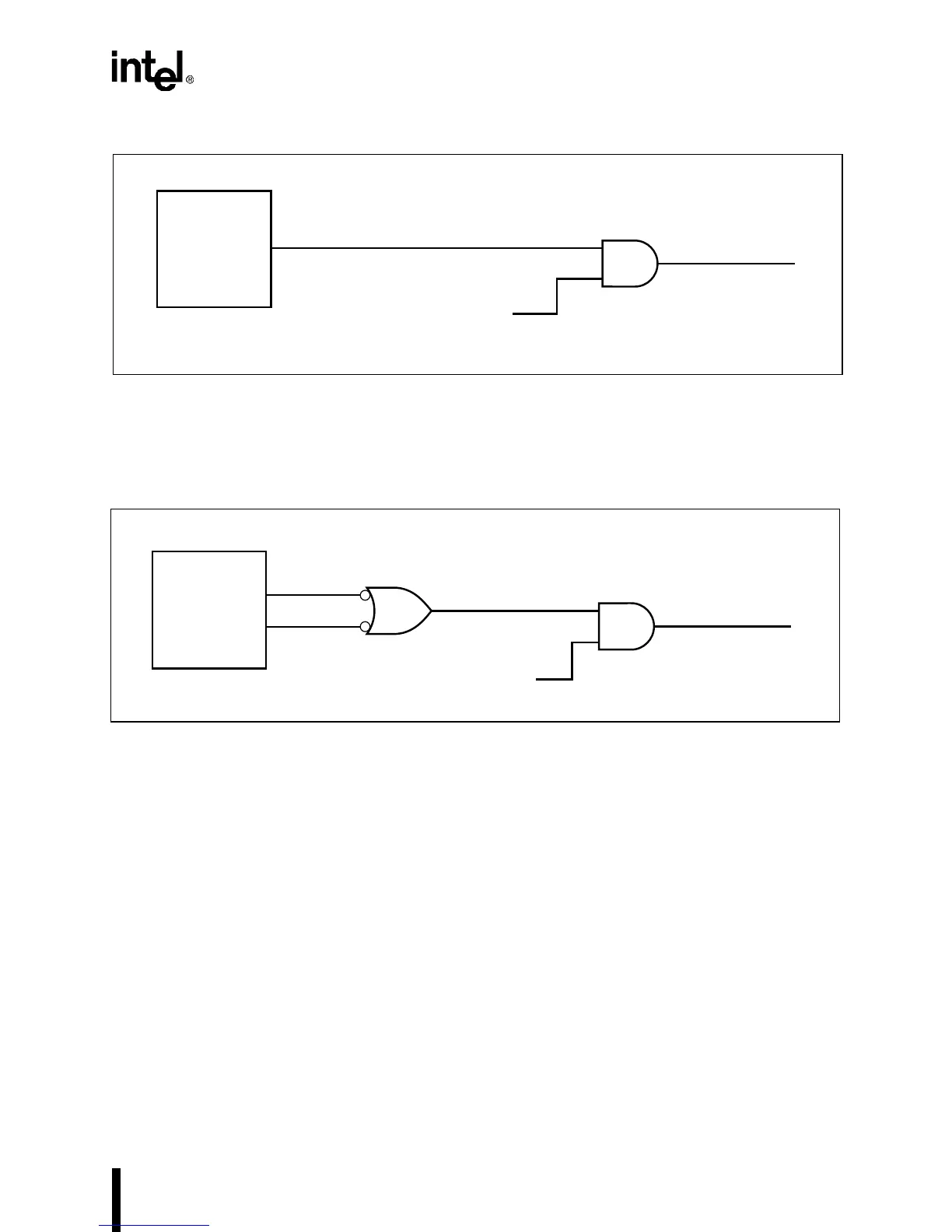

For systems based on Intel386 EX processor, the AEN signal could be derived as shown in Figure

B-2. Notice that since the DMA acknowledge signals are used instead of a generic HLDA, there

is no need to incorporate the REFRESH# signal in the logic.

Figure B-2. Derivation of AEN Signal for Intel386™ EX processor-based Systems

In a PC/AT system using the 8237A DMA controller in fly-by mode, the 8237A generates appro-

priate control signals for memory (MEMR# or MEMW#) and for I/O (IOW# and IOR#). The

Intel386 EX processor’s internal DMA, during fly-by transfers, generates control signals (M/IO#

and W/R#) that apply to the memory device. There needs to be some external logic that can detect

the DMA operation (through the AEN signal) and generate a complementary I/O cycle. For ex-

ample, if the DMA is generating a memory read cycle and AEN is active, then the logic should

drive the IOW# signal on the PC/AT bus. Actually, the internal DMA could be programmed in a

two-cycle mode eliminating the need for external logic. This will not have a significant impact

on the performance — of the two cycles required to complete the transfer, the I/O cycle is the long

one (meeting PC/AT timings) while the memory cycle is relatively very quick.

The drive capability and the operating frequency of the Intel386 EX processor signals are differ-

ent from the standard PC/AT bus, which requires 24 mA drive capacity at 200 pF capacitive load.

Most PC/AT systems presently operate in a “quiet bus” mode so that non-ISA cycles are not re-

flected on the ISA bus. In a typical implementation, the address/data buses may change states, but

the control signals are not strobed if a non-ISA cycle is detected. External three-state buffers and

some decoding logic are needed to implement this scheme. The EV386EX (evaluation board for

A2504-01

HLDA

MASTER#

(From PC/AT* Bus)

AEN

Processor

A2503-01

Processor

DACK0#

DACK1#

DACK

MASTER# (From PC/AT* Bus)

AEN

Loading...

Loading...