17-7

WATCHDOG TIMER UNIT

17.4 REGISTER DEFINITIONS

This section describes the registers associated with the WDT, and explains how these registers

can be used to enable and use each WDT mode.

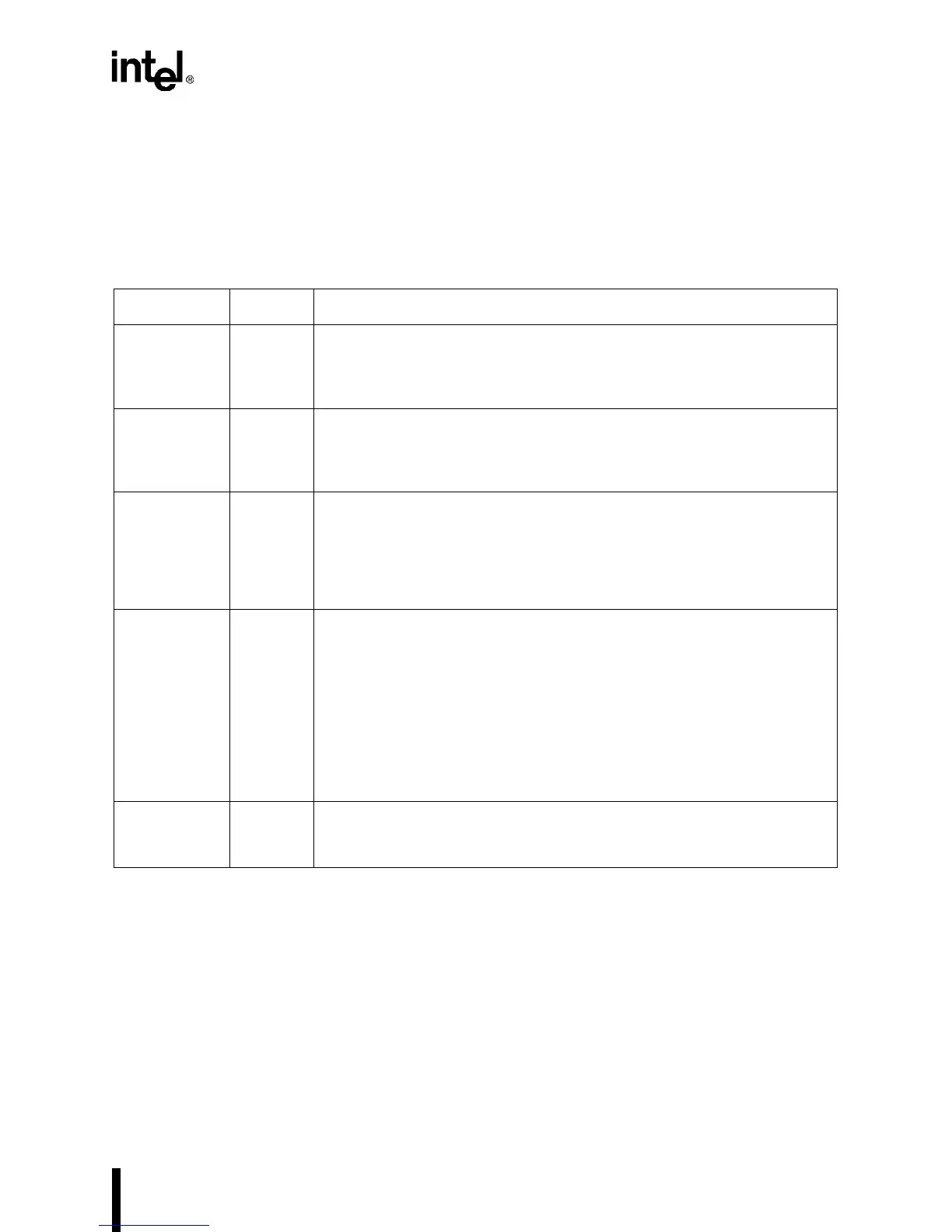

Table 17-2 describes the registers associated with the WDT.

Table 17-2. WDT Registers

Register Address Description

WDTCLR 0F4C8H Watchdog Timer Clear:

Write the lockout sequence to this location. Circuitry at this address decodes

the lockout sequence to enable watchdog mode, reload the counter, or both.

This location is used only for watchdog mode.

WDTCNTH

WDTCNTL

(read only)

0F4C4H

0F4C6H

WDT Counter:

These registers hold the current value of the WDT down-counter. Software

can read them to determine the current count value. Any reload event

reloads these registers with the contents of WDTRLDH and WDTRLDL.

WDTRLDH

WDTRLDL

(read/write)

0F4C0H

0F4C2H

WDT Reload Value:

Write the reload value to these registers, using two word writes. After a

lockout sequence is issued, these registers cannot be written again until after

a device reset. A reload event (each WDT mode has its own; refer to

Sections 17.2.2 through 17.2.4) reloads WDTCNTH and WDTCNTL with the

contents of these registers.

WDTSTATUS

(read/write)

0F4CAH WDT Status:

This register contains one read-only bit (WDTEN) that indicates whether

watchdog mode is enabled and two read/write bits that control bus monitor

mode and the WDT clock. A lockout sequence sets the WDTEN bit and

clears the two read/write bits, disabling bus monitor mode and enabling the

WDT clock. After a lockout sequence is issued, a write to this register has no

effect unless the device is reset.

Software can read this register to determine the current status of the WDT

and (unless a lockout sequence has been issued) can set the BUSMON bit to

enable bus monitor mode or set the CLKDIS bit to disable the WDT.

PWRCON

(read/write)

0F800H Power Control register:

This register holds the WDTRDY bit that is used to enable/disable internal

READY# generation for the WDT Bus Monitor mode.

Loading...

Loading...