Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

7-12

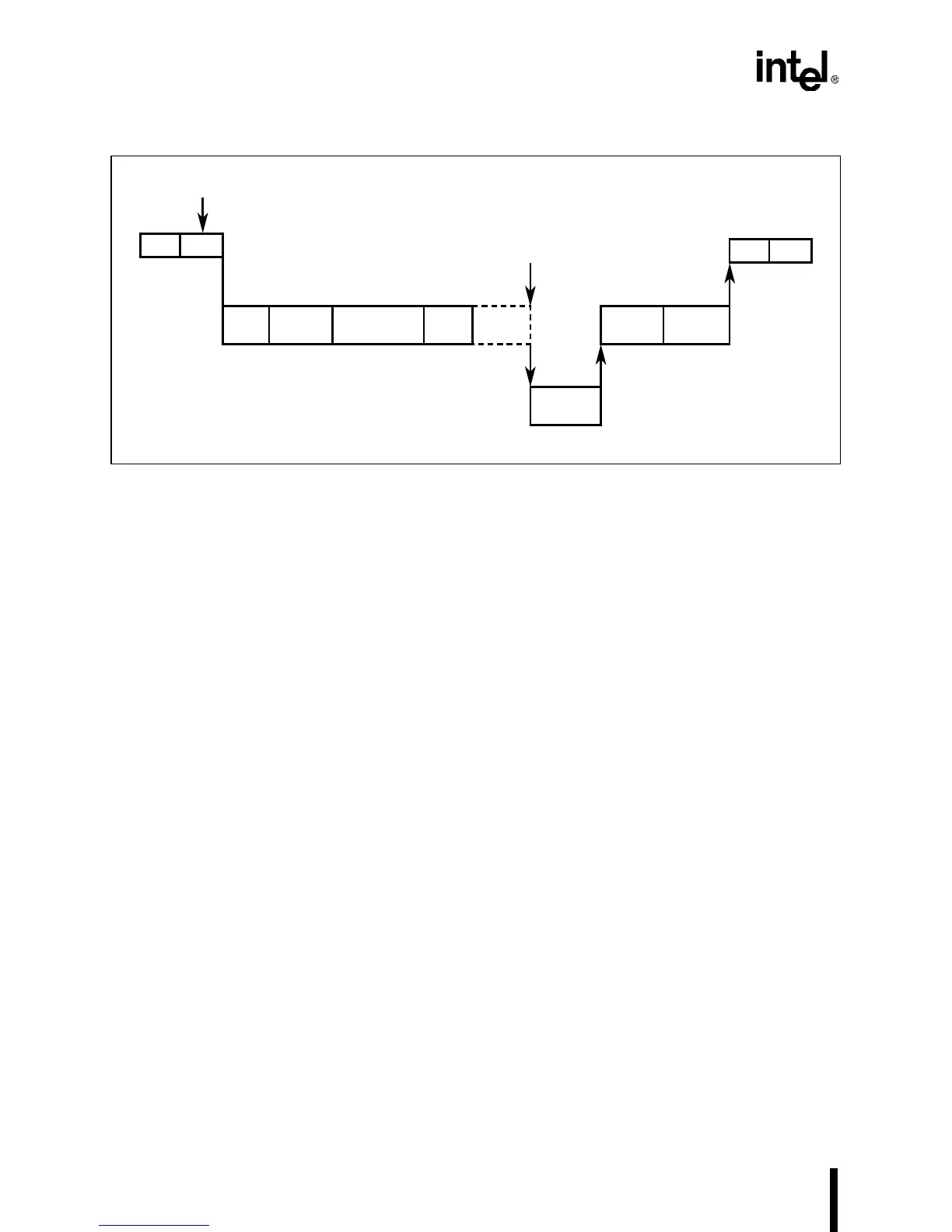

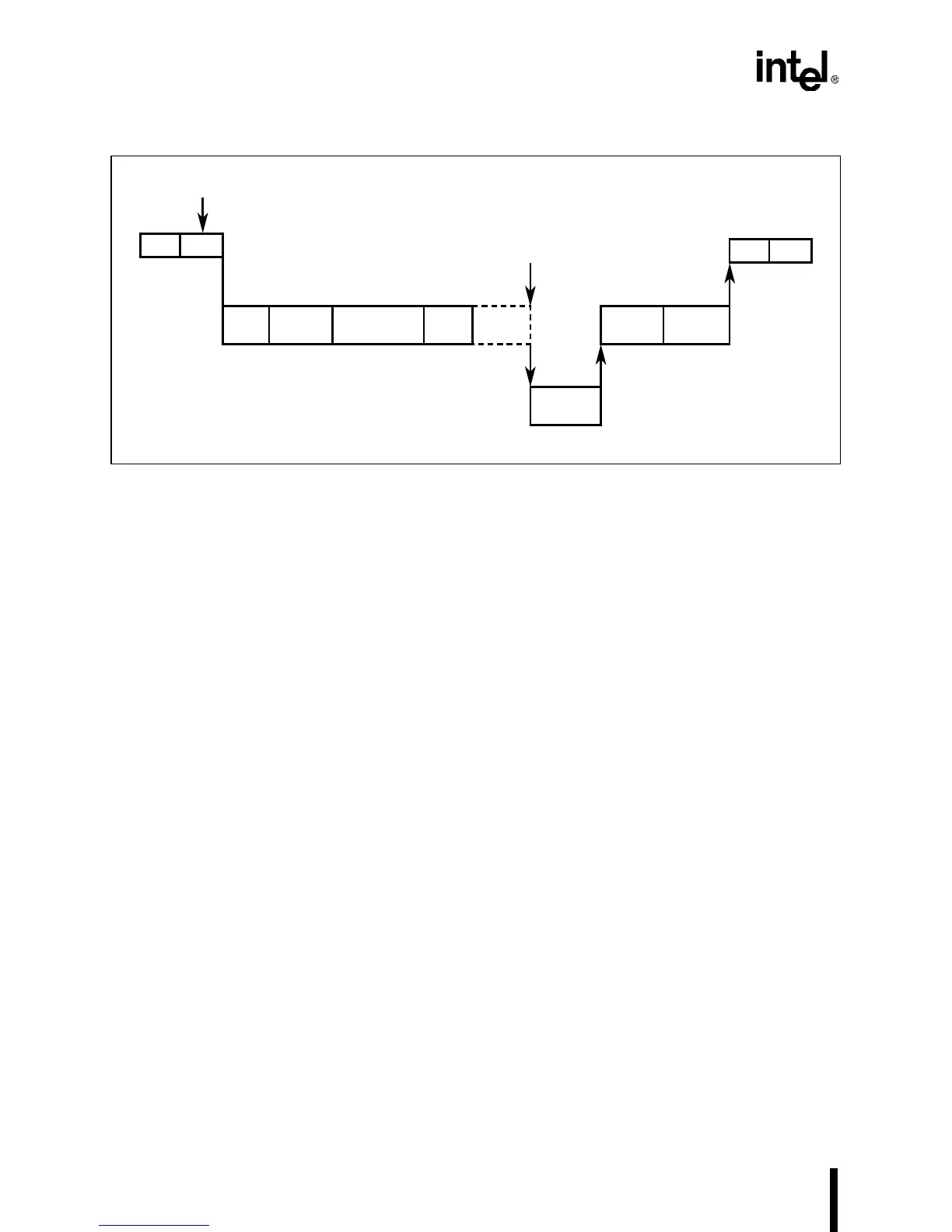

Figure 7-7. HALT During SMM Handler

7.3.3.3 Idle Mode and Powerdown Mode During SMM

Both Idle Mode and Powerdown Mode may be used while in SMM. Entering and exiting either

of these power management modes from SMM is identical to entering or exiting from normal

mode. The interaction between SMM and power management modes is described in Chapter 8.

7.3.3.4 SMI# During SMM Operation

If the SMI# request is asserted during SMM operation, the second SMI# cannot nest the currently

executing SMM. The second SMI# request is latched, and held pending by the CPU. Only one

SMI# request can be pending. After RSM execution is completed, the pending SMI# is serviced.

At this time, SMIACT# is deasserted once at completion of RSM, then asserted again for the sec-

ond SMI#.

When the SMM handler polls the various SMI# sources for one of the SMI# triggers, and two

SMI# sources are found in the SMI# generation circuit, the SMM handler services both SMI#

sources and executes a RSM instruction. In this SMM handler, if the SMI# generation circuit as-

serts the second SMI# during the first SMI# service routine, the second SMI# is pending. Next,

the SMM handler finds and services two SMI# sources. After the CPU completes the RSM exe-

cution, the pending SMI# (second SMI#) is generated, but there is nothing to service because the

second SMI# was serviced during the first SMM handler. This unnecessary SMI# transaction re-

quires a few hundred clocks. There may be some performance degradation if this example occurs

frequently. For good performance, it is the responsibility of the SMI# generation circuitry to man-

age multiple SMI# assertions.

7.3.4 SMRAM Programming

7.3.4.1 Chip-select Unit Support for SMRAM

The internal chip-select unit (CSU) has been extended to support the SMRAM by using bit 10 in

each Low Address (CASMM) and Low Mask register (CMSMM). The CSU acts on these bits

A2507-01

State

Save

SMI#

SMM

Handler

Instr

Instr

Enable

INTR & NMI

HALT Halted

State

SMM

Handler

State

Resume

Instr Instr

Interrupt

Handler

INTR or NMI

#1 #2

#3 #4

Loading...

Loading...