9-25

INTERRUPT CONTROL UNIT

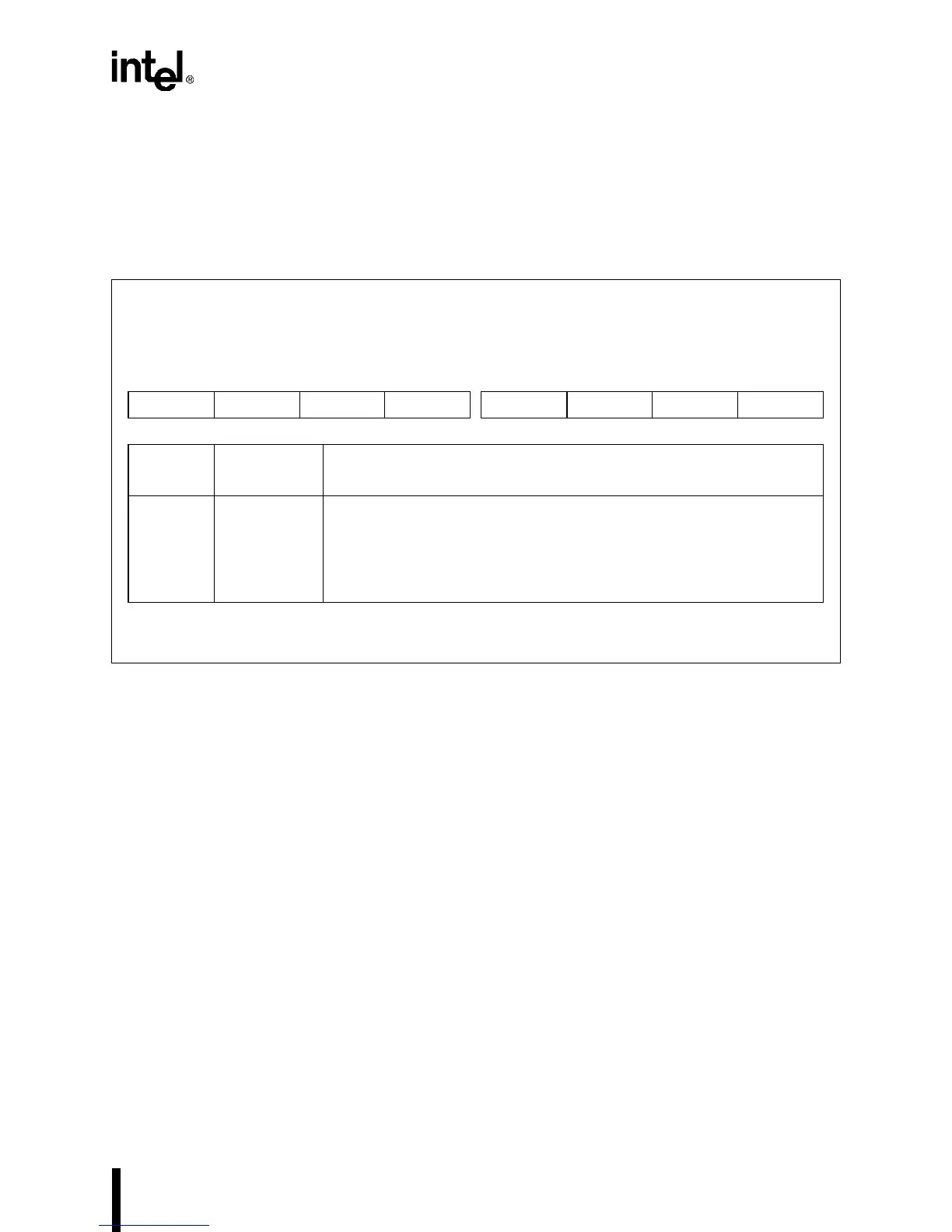

9.3.7 Operation Command Word 1 (OCW1)

OCW1 is the interrupt mask register. Setting a bit in the interrupt mask register disables (masks)

interrupts from the corresponding IR signal. For example, setting the master’s OCW1 M3 bit dis-

ables interrupts from the master IR3 signal. Clearing a bit in the interrupt mask register enables

interrupts from the corresponding IR signal.

Figure 9-13. Operation Command Word 1 (OCW1)

Operation Command Word 1

OCW1 (master and slave)

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

master slave

F021H F0A1H

0021H 00A1H

XXH XXH

7 0

M7 M6 M5 M4 M3 M2 M1 M0

Bit

Number

Bit

Mnemonic

Function

7–0 M7:0 Mask IR:

0 = Enables interrupts on the corresponding IR signal.

1 = Disables interrupts on the corresponding IR signal.

NOTE: Setting the mask bit does not clear the respective interrupt

pending bit.

NOTE: The 8259A must be initialized before it can be used. After reset, the 8259A register states are

undefined. The 8259A modules must be initialized before the IF flag in the core FLAG register is

set.

Loading...

Loading...