10-33

TIMER/COUNTER UNIT

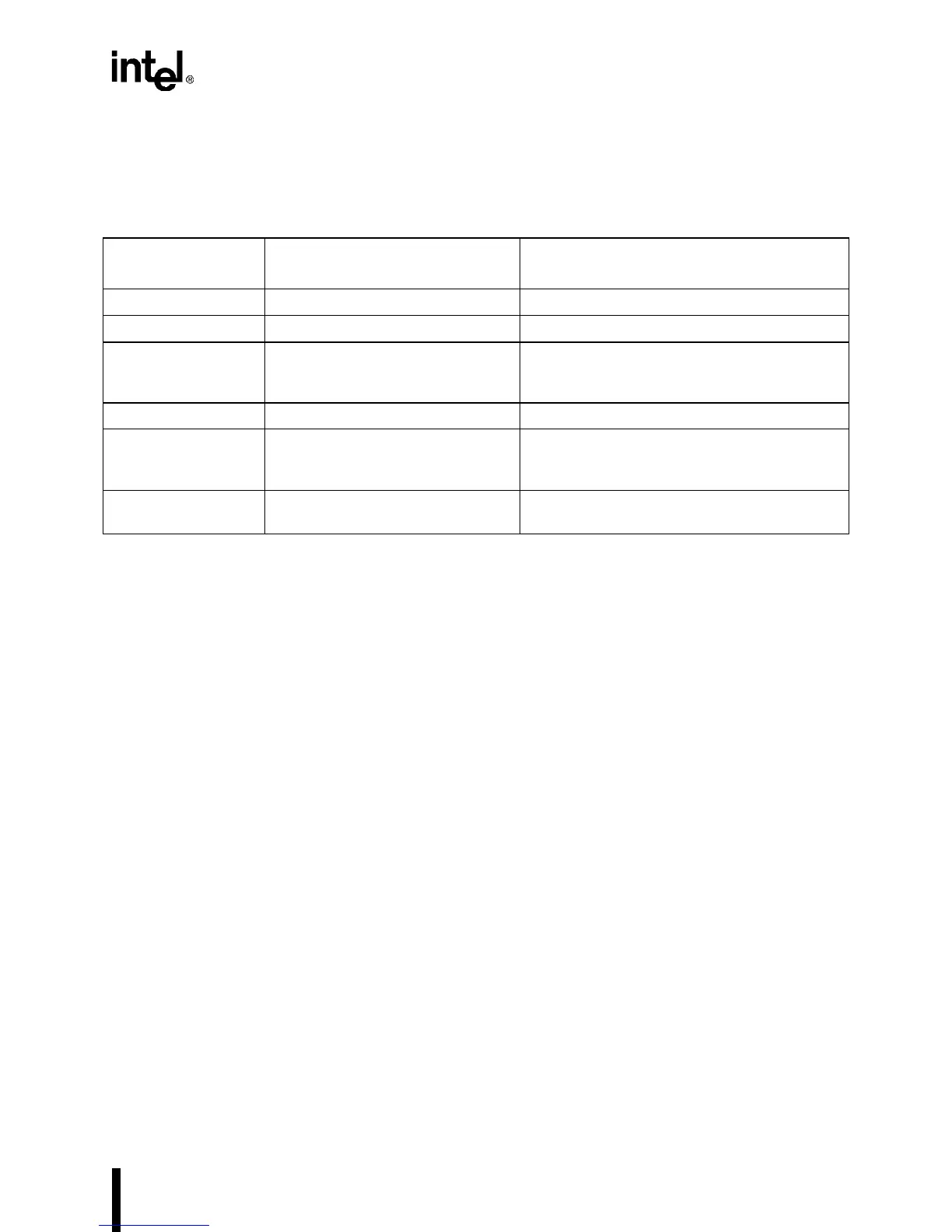

When a counter receives multiple read-back commands, it ignores all but the first command; the

count/status that the core reads is the count/status latched from the first read-back command (see

Table 10-6).

10.4 PROGRAMMING CONSIDERATIONS

Consider the following when programming the TCU.

• The 16-bit counters are read and written a byte at a time. The control word format of

TMRCON selects whether you read or write the least-significant byte only, most-significant

byte only, or least-significant byte then most-significant byte (this is called the counter’s

read/write selection). You must read and write the counters according to their programmed

read/write selections.

• When you program a counter for the two-byte read or write selection, you must read or

write both bytes. If you’re using more than one subroutine to read or write a counter, make

sure that each subroutine reads or writes both bytes before transferring control.

• You can program the counters for either an internal or external clock source (to CLKINn).

The internal source is a prescaled value of the processor clock and therefore, is turned off in

the processor’s powerdown mode (processor clock is off). If an external clock source is

used, it is not affected by the processor’s powerdown mode, because the clock signal is

provided by an off-chip source. “Controlling Power Management Modes” on page 8-8

describes the processor’s powerdown and idle modes.

Table 10-6. Results of Multiple Read-back Commands Without Reads

Command

Sequence

Read-back Command Command Result

1 Latch counter 0’s count and status. Counter 0’s count and status latched.

2 Latch counter 1’s status. Counter 1’s status latched.

3 Latch counter 2 and 1’s status. Counter 2’s status latched; counter 1’s status

command ignored because command 2

already latched its status.

4 Latch counter 2’s count. Counter 2’s count latched.

5 Latch counter 1’s count and status. Counter 1’s count latched; counter 1’s status

command ignored because command 2

already latched its status.

6 Latch counter 0’s count. Counter 0’s count command ignored because

command 1 already latched its count.

Loading...

Loading...