11-15

ASYNCHRONOUS SERIAL I/O UNIT

11.3 REGISTER DEFINITIONS

Table 11-5 lists the registers associated with the SIO unit and the following sections contain bit

descriptions for each register.

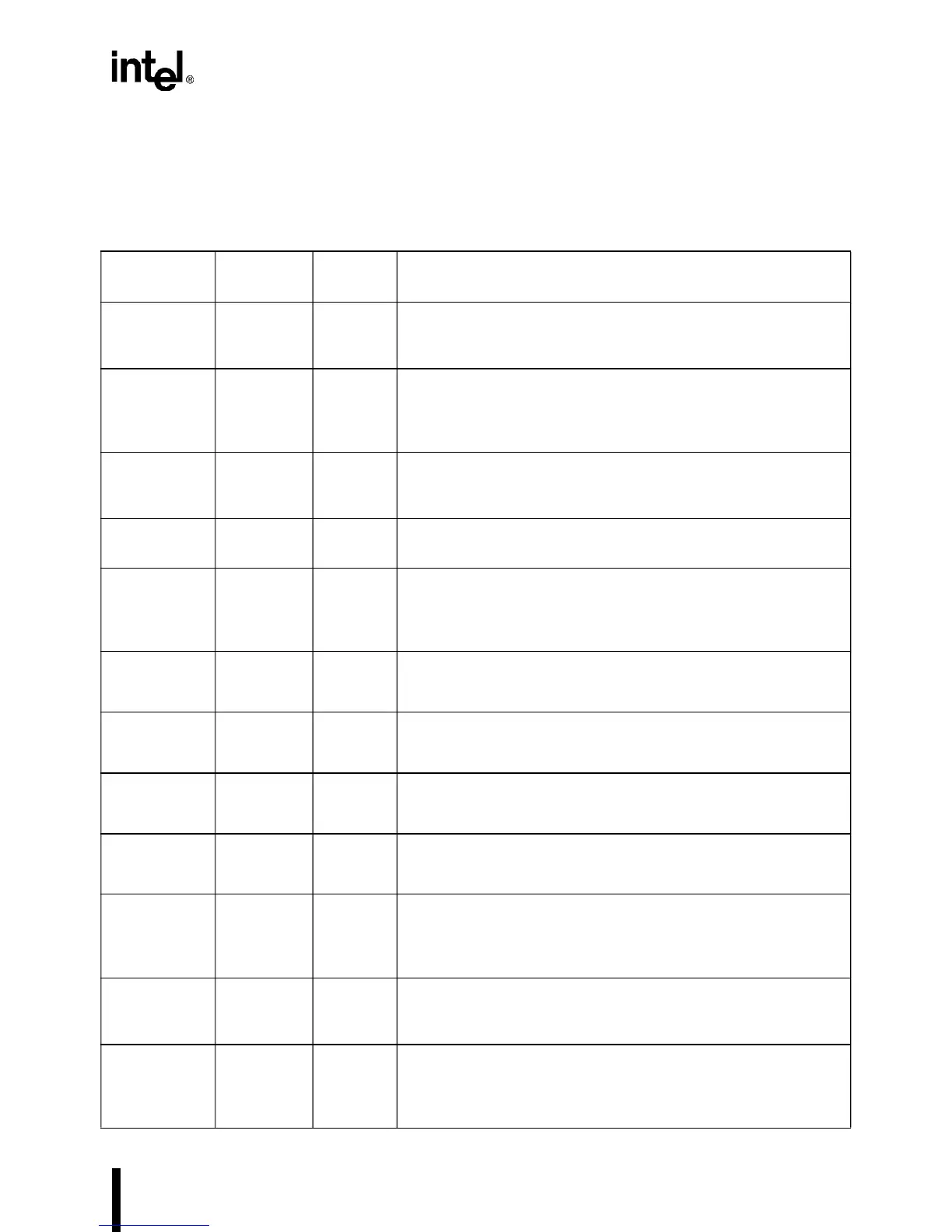

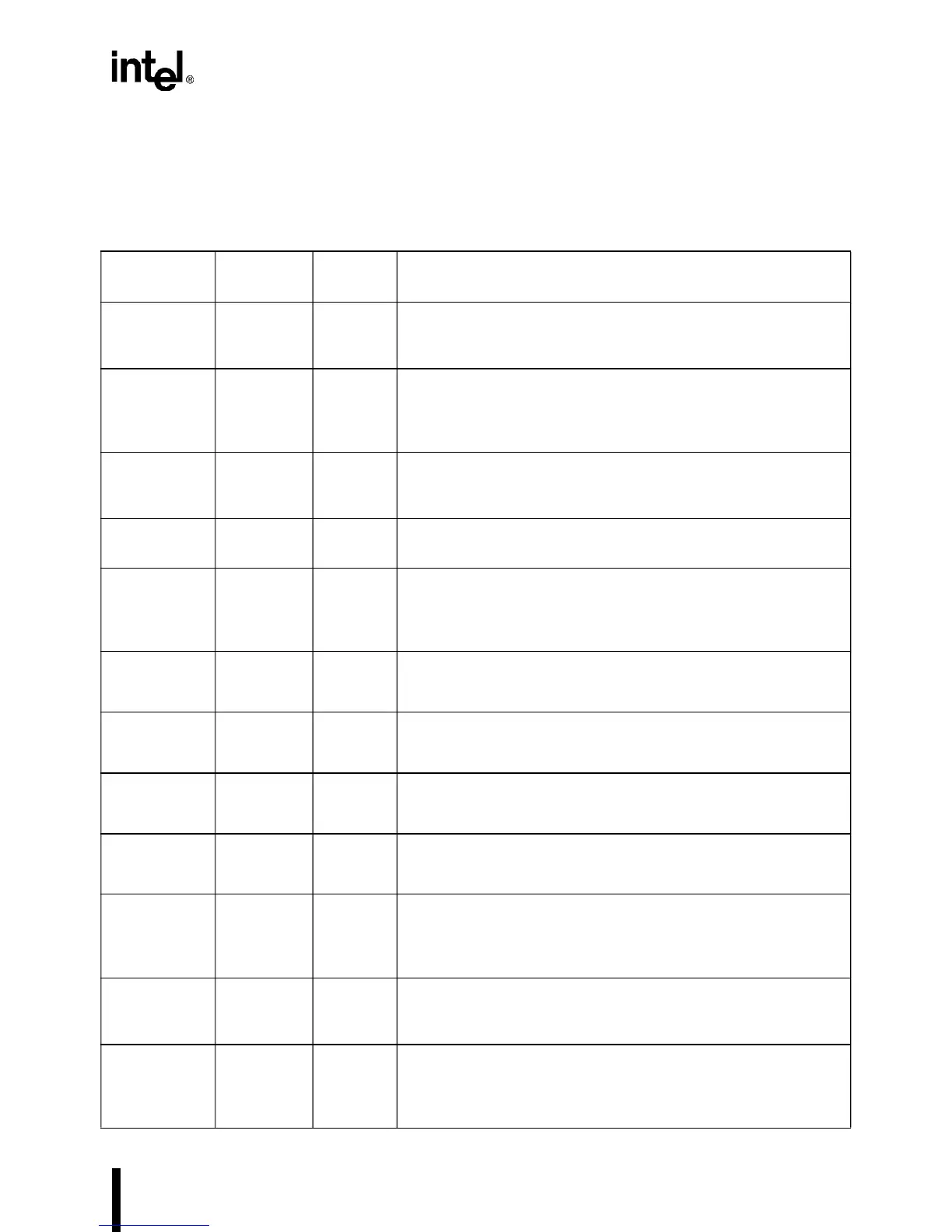

Table 11-5. SIO Registers (Sheet 1 of 2)

Register

Expanded

Address

PC/AT*

Address

Function

PINCFG

(read/write)

0F826H — Pin Configuration:

Connects the SIO1 transmit data (TXD1), data terminal ready

(DTR1#), and request to send (RTS1#) signals to package pins.

P1CFG

(read/write)

0F820H — Port 1 Configuration:

Connects the SIO0 ring indicator (RI0#), data set ready (DSR0#),

data terminal ready (DTR0#), request to send (RTS0#), and data

carrier detected (DCD0#) signals to package pins.

P2CFG

(read/write)

0F822H — Port 2 Configuration:

Connects the SIO0 clear to send (CTS0#), transmit data (TXD0),

and receive data (RXD0) signals to package pins.

P3CFG

(read/write)

0F824H — Port 3 Configuration:

Connects COMCLK to the package pin.

SIOCFG

(read/write)

0F836H — SIO and SSIO Configuration:

Connects the SIO

n

modem input signals internally or to package

pins and connects either the internal SERCLK signal or the

COMCLK pin to the SIO

n

baud-rate generator input.

DLL0

DLL1

(read/write)

0F4F8H

0F8F8H

03F8H

02F8H

Divisor Latch Low:

Stores the lower 8 bits of the SIO

n

baud-rate generator divisor.

DLH0

DLH1

(read/write)

0F4F9H

0F8F9H

03F9H

02F9H

Divisor Latch High:

Stores the upper 8 bits of the SIO

n

baud-rate generator divisor.

TBR0

TBR1

(write only)

0F4F8H

0F8F8H

03F8H

02F8H

Transmit Buffer:

Holds the data byte to transmit.

RBR0

RBR1

(read only)

0F4F8H

0F8F8H

03F8H

02F8H

Receiver Buffer:

Holds the data byte received.

LCR0

LCR1

(read/write)

0F4FBH

0F8FBH

03FBH

02FBH

Line Control:

Specifies the data frame (word length, number of stop bits, and

type of parity) for transmissions and receptions. Allows the

transmitter to transmit a break condition.

LSR0

LSR1

(read only)

0F4FDH

0F8FDH

03FDH

02FDH

Line Status:

Contains the transmitter empty, transmit buffer empty, receive

buffer full, and receive error flags.

IER0

IER1

(read/write)

0F4F9H

0F8F9H

03F9H

02F9H

Interrupt Enable:

Independently connects the four signals (modem status, receive

line status, transmit buffer empty, and receive buffer full) to the

interrupt request output (SIOINT

n

).

Loading...

Loading...