Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

17-2

READY#). In bus monitor mode, the ADS# signal from the bus interface unit (BIU) reloads the

down-counter and the READY# signal stops it. The READY# signal can be generated either ex-

ternally or internally, using the WDTRDY bit in the PWRCON register (Figure 17-5). If this bit

is deasserted, then an external READY# is required to terminate the cycle when the WDT times

out (WDTOUT is asserted) in Bus Monitor mode. In this case, if a READY# is never generated

by external logic, the processor hangs (since the bus cycle never terminates). If the WDTRDY bit

is set, the processor generates an internal READY# to terminate the cycle upon time-out

(WDTOUT is asserted) in Bus Monitor mode.

The WDT circuitry correctly matches each READY# with a corresponding ADS# (even in pipe-

lined mode when two ADS# pulses occur before the first READY# pulse).

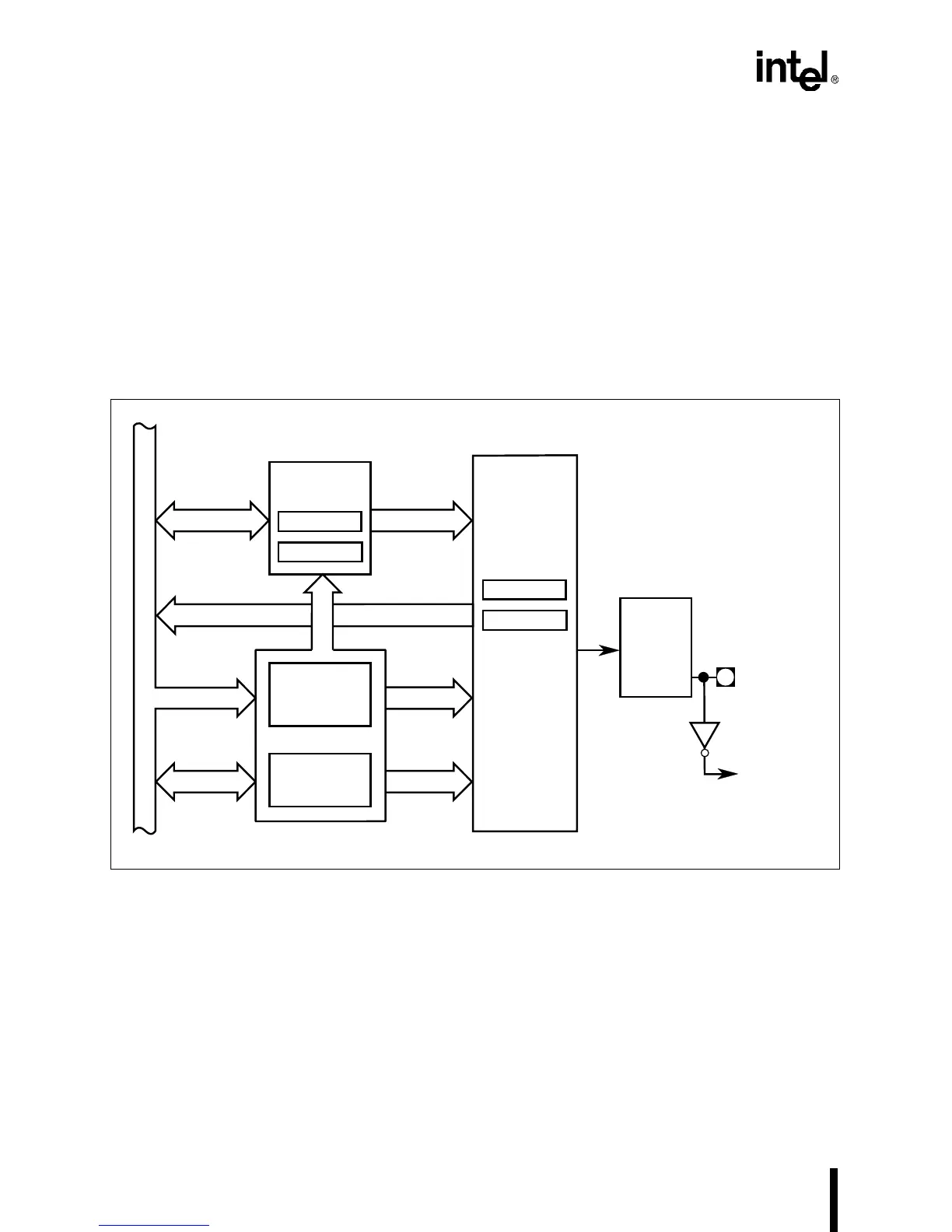

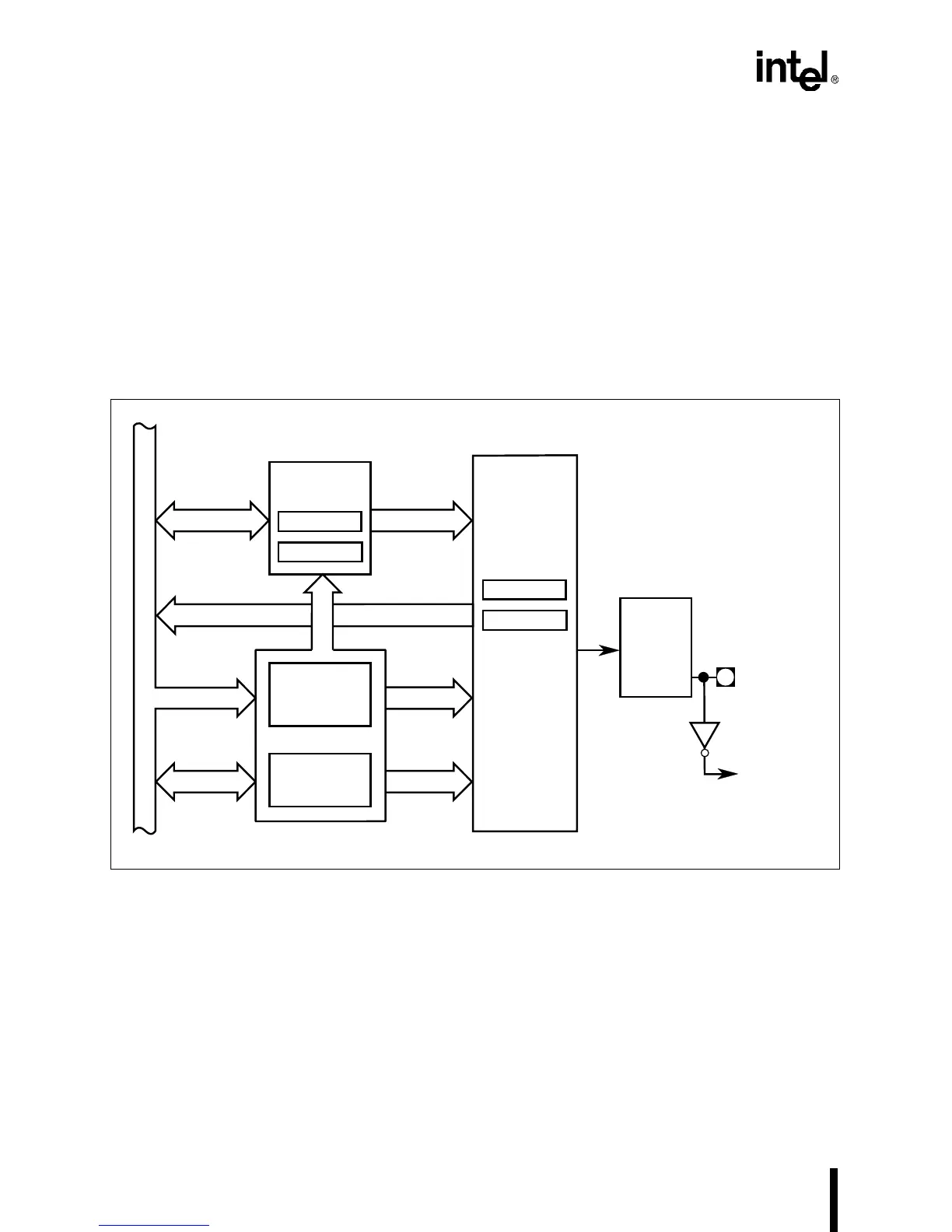

Figure 17-1. Watchdog Timer Unit Connections

E

I

B

u

s

A2330-02

Reload

Registers

WDTRLDH

WDTRLDL

32-Bit

Down Counter

WDTCLR

Connect

to NMI

or RESET

8-State

Binary

Counter

WDTOUT

WDTSTATUS

WDTCNTH

WDTCNTL

WDTOUT#

to IR7 of

Slave 8259A

Loading...

Loading...