14 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 1: Transceiver and Tool Overview

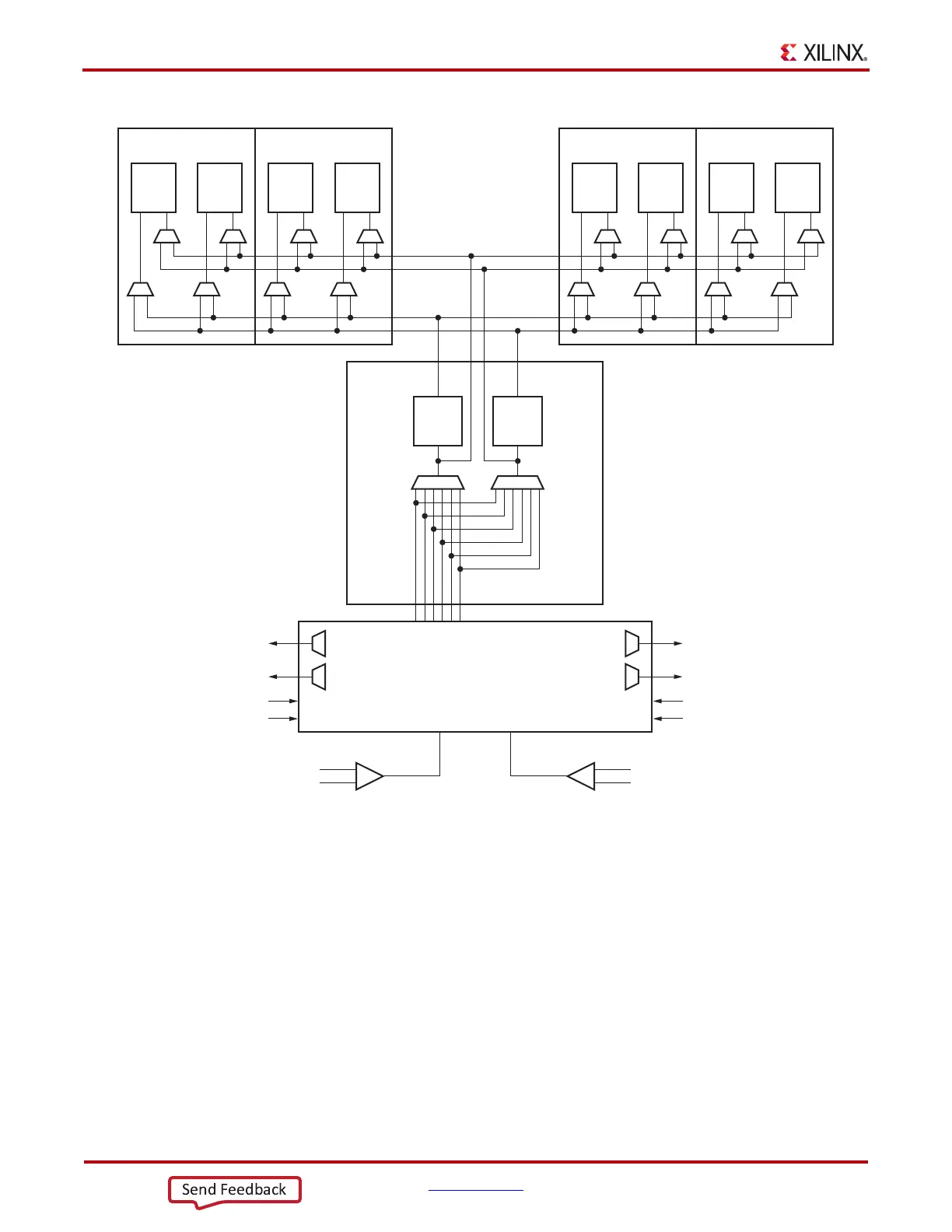

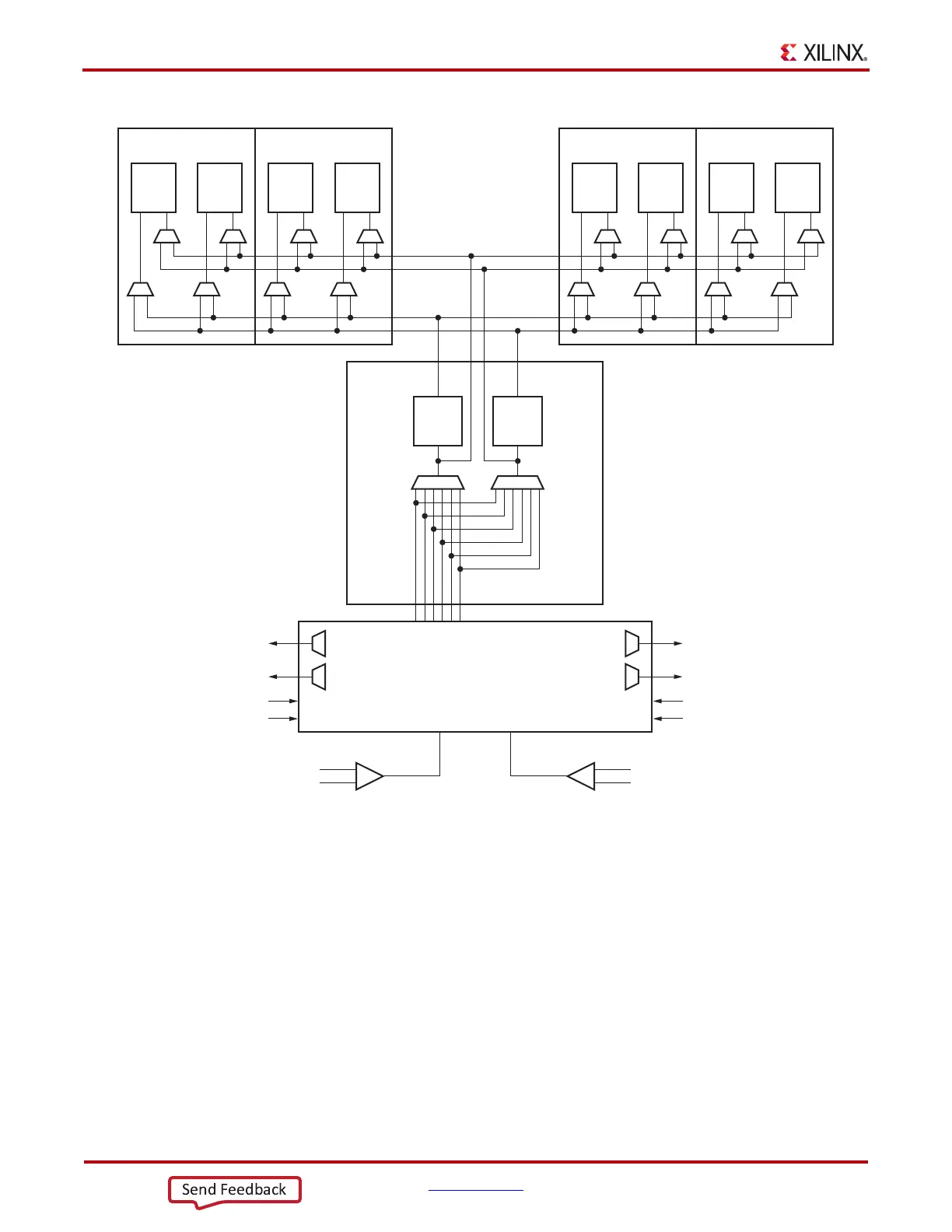

Four GTPE2 channels clustered together with one GTPE2_COMMON primitive are called a Quad

or Q.

The GTPE2_COMMON primitive contains two ring oscillator PLLs (PLL0 and PLL1).

GTPE2_COMMON must always be instantiated.

Each GTPE2_CHANNEL primitive consists of a transmitter and a receiver.

X-Ref Target - Figure 1-2

Figure 1-2: GTP Transceiver Quad Configuration

UG482_c1_02_110811

RX TX

GTPE2_CHANNEL

RX TX

GTPE2_CHANNEL

PLL0

RX TX

GTPE2_CHANNEL

GTPE2_COMMON

REFCLK Distribution

PLL1

RX TX

GTPE2_CHANNEL

IBUFDS_GTE2 IBUFDS_GTE2

Loading...

Loading...