7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 13

UG482 (v1.9) December 19, 2016

Overview and Features

Additional information on the functional blocks of 7 series FPGAs is available at:

UG470, 7 Series FPGAs Configuration User Guide provides more information on the

configuration.

UG471

, 7 Series FPGAs SelectIO Resources User Guide provides more information on the I/O

blocks.

UG472

, 7 Series FPGAs Clocking Resources User Guide provides more information on the

mixed mode clock manager (MMCM).

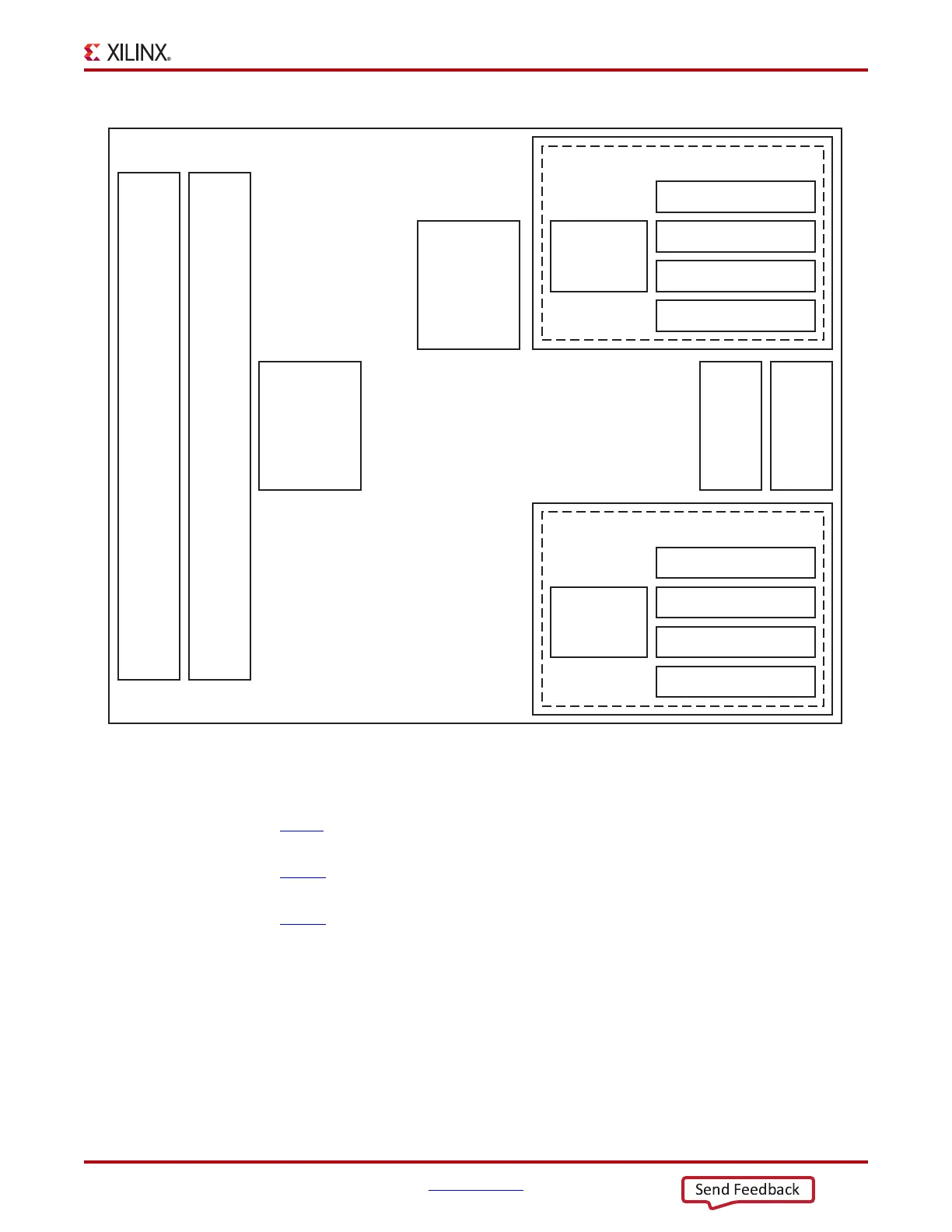

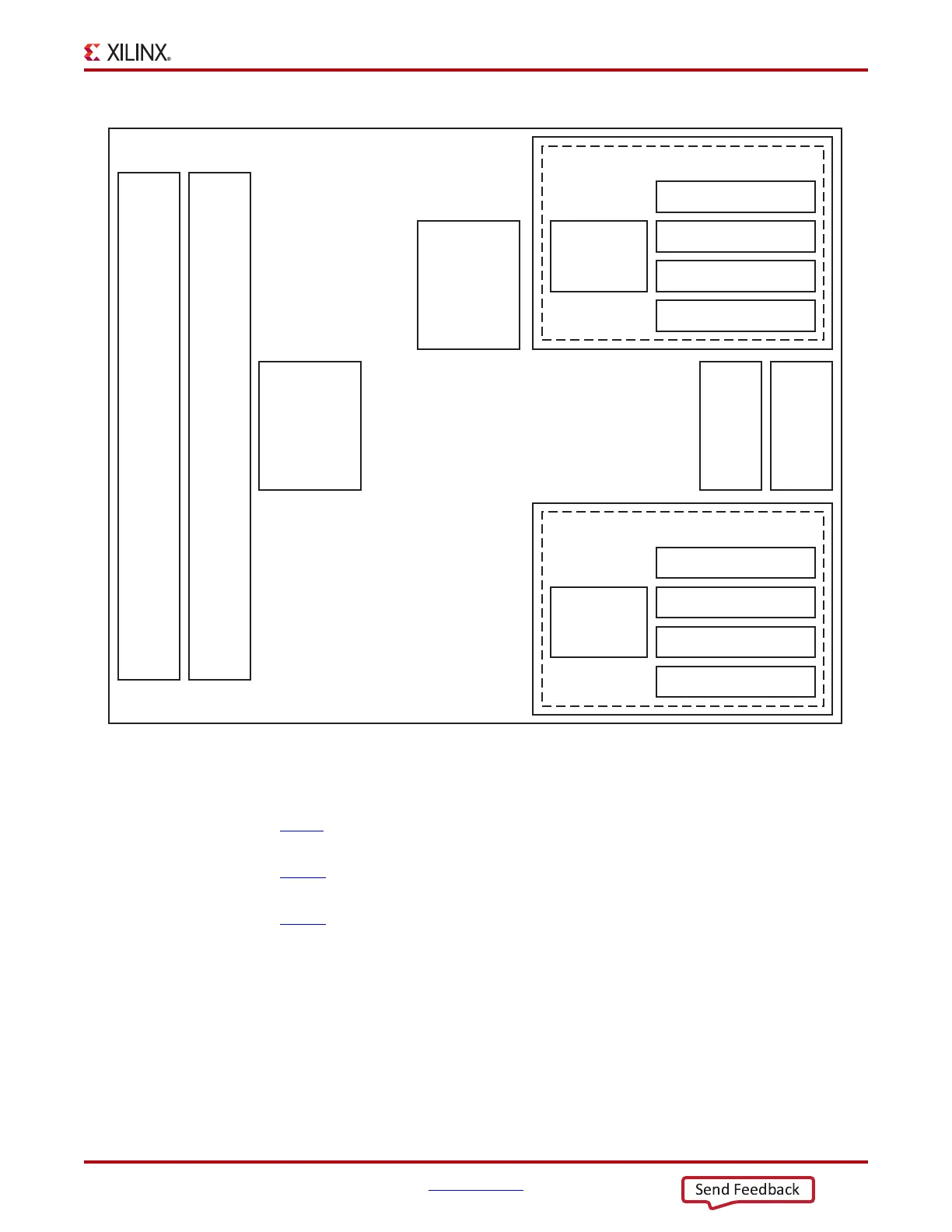

Figure 1-2 illustrates the clustering of four GTPE2_CHANNEL primitives and one

GTPE2_COMMON primitive to form a Quad.

X-Ref Target - Figure 1-1

Figure 1-1: GTP Transceiver Inside Artix-7 XC7A100T FPGA

I/O

Column

CMT

Column

I/O

Column

GTPE2_CHANNEL_X0Y7

GTPE2_CHANNEL_X0Y6

GTPE2_

COMMON_

X0Y1

GTPE2_CHANNEL_X0Y5

GTPE2_CHANNEL_X0Y4

CMT

Column

GTP Quad

Artix-7 FPGA (XC7A100T)

GTPE2_CHANNEL_X0Y3

GTPE2_CHANNEL_X0Y2

GTPE2_

COMMON_

X0Y0

GTPE2_CHANNEL_X0Y1

GTPE2_CHANNEL_X0Y0

GTP Quad

Configuration

Integrated

Block for PCI

Express

Operation

UG482_C1_01_110811

Loading...

Loading...