7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 159

UG482 (v1.9) December 19, 2016

RX Pattern Checker

Ports and Attributes

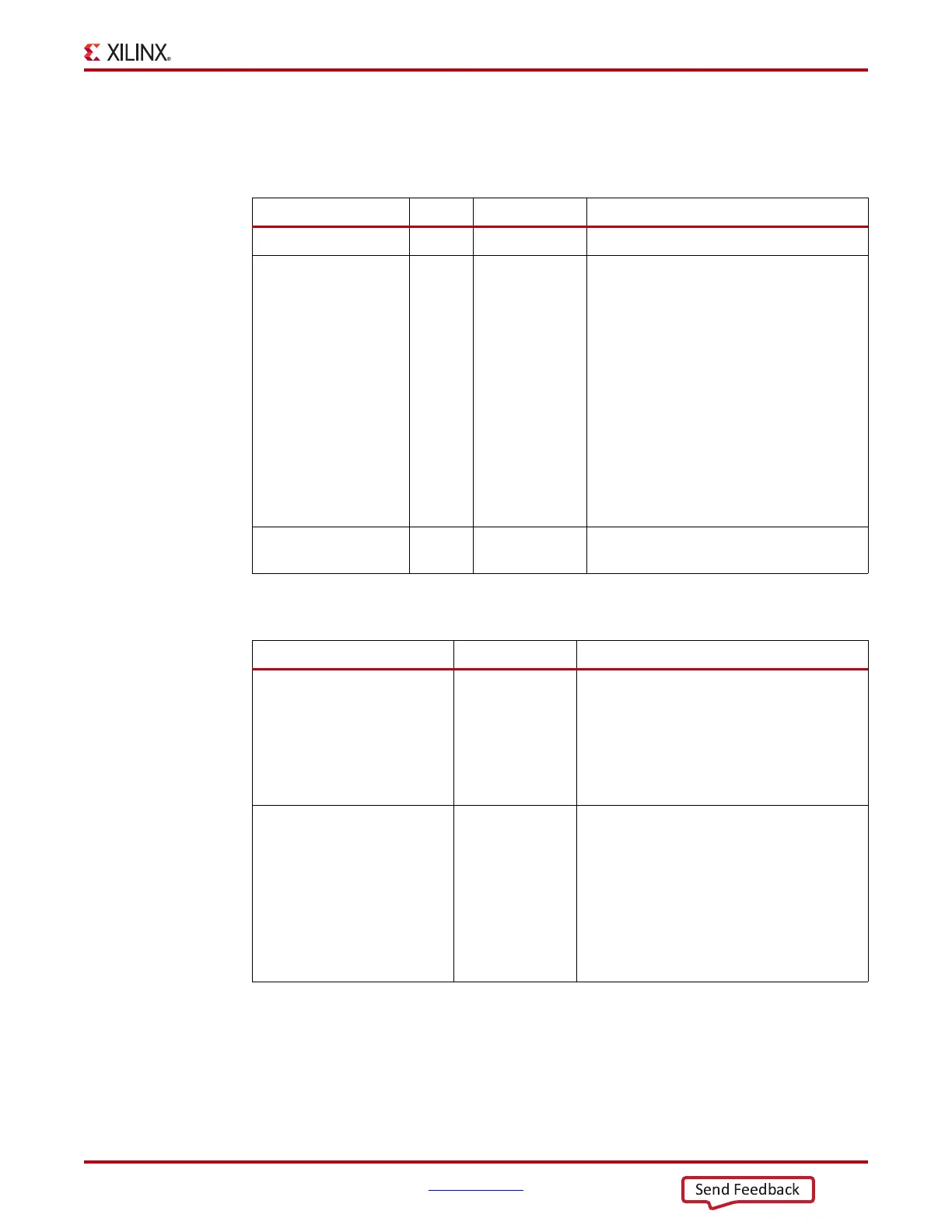

Table 4-23 defines the pattern checker ports.

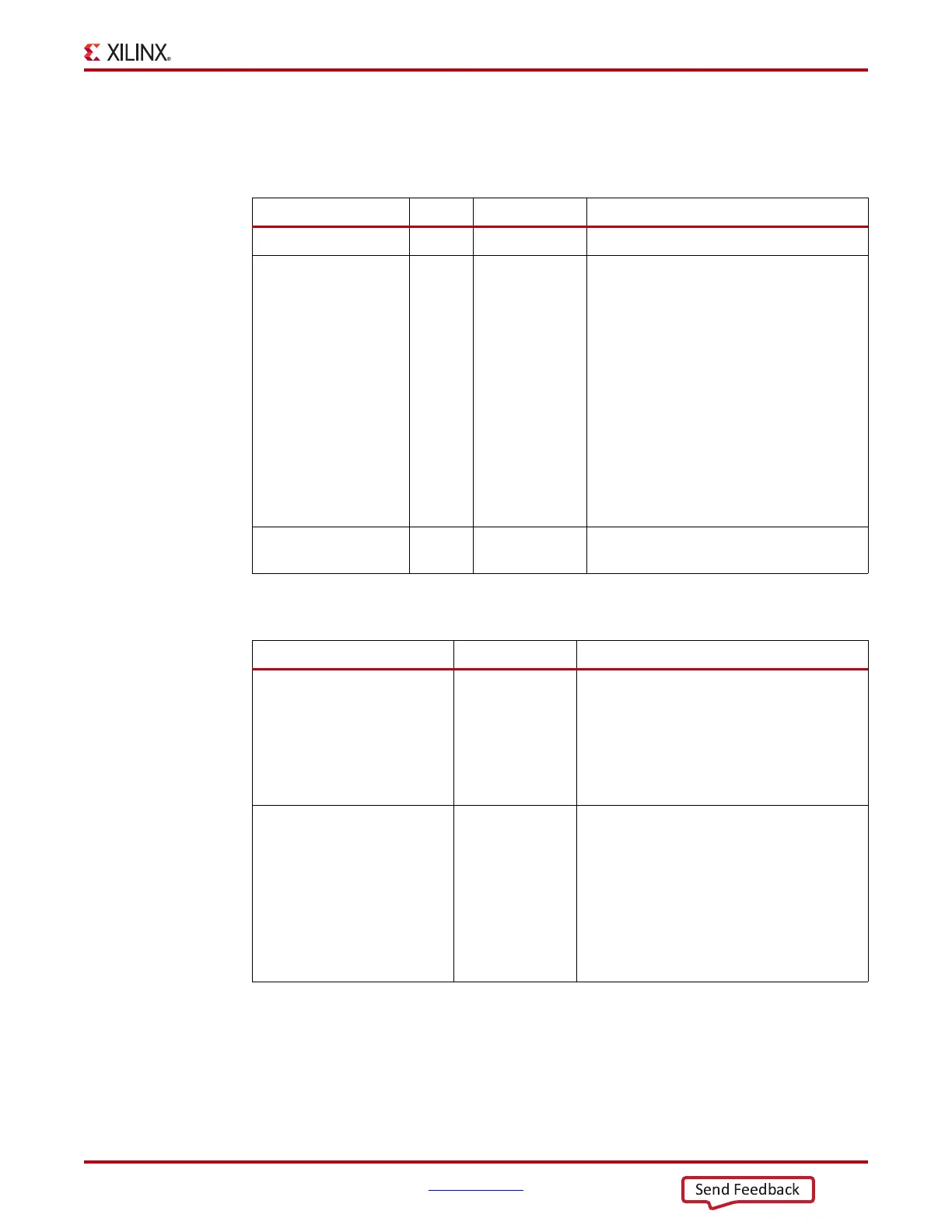

Table 4-24 defines the pattern checker attributes.

Use Models

To use the built-in PRBS checker, RXPRBSSEL must be set to match the PRBS pattern being sent

to the receiver. The RXPRBSSEL entry in Table 4-23 shows the available settings. When the PRBS

checker is running, it attempts to find the selected PRBS pattern in the incoming data. If the

incoming data is inverted by the transmitter or reversed RXP/RXN, the received data should also

Table 4-23: Pattern Checker Ports

Port Dir Clock Domain Description

RXPRBSCNTRESET In RXUSRCLK2 Resets the PRBS error counter.

RXPRBSSEL[2:0] In RXUSRCLK2 Receiver PRBS checker test pattern control.

Only these settings are valid:

000: Standard operation mode. (PRBS

check is off)

001: PRBS-7

010: PRBS-15

011: PRBS- 23

100: PRBS-31

No checking is done for non-PRBS patterns.

Single bit errors cause bursts of PRBS errors

because the PRBS checker uses data from the

current cycle to generate next cycle's

expected data.

RXPRBSERR Out RXUSRCLK2 This non-sticky status output indicates that

PRBS errors have occurred.

Table 4-24: Pattern Checker Attributes

Attribute Type Description

RX_PRBS_ERR_CNT 16-bit Binary PRBS error counter. This counter can be reset

by asserting RXPRBSCNTRESET. When an

error(s) in incoming parallel data occurs, this

counter increments by 1 and counts up to

0xFFFF. This error counter can only be

accessed via the DRP. The address for this

counter is 0x15E.

RXPRBS_ERR_LOOPBACK 1-bit Binary When this attribute is set to 1, the

RXPRBSERR bit is internally looped back to

TXPRBSFORCEERR of the same GTP

transceiver. This allows synchronous and

asynchronous jitter tolerance testing without

worrying about data clock domain crossing.

When this attribute is set to 0,

TXPRBSFORCEERR is forced onto the TX

PRBS.

Loading...

Loading...