192 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

Ports and Attributes

Table 4-36 defines the ports required by RX clock correction functions.

Table 4-37 defines the attributes required by RX channel bonding.

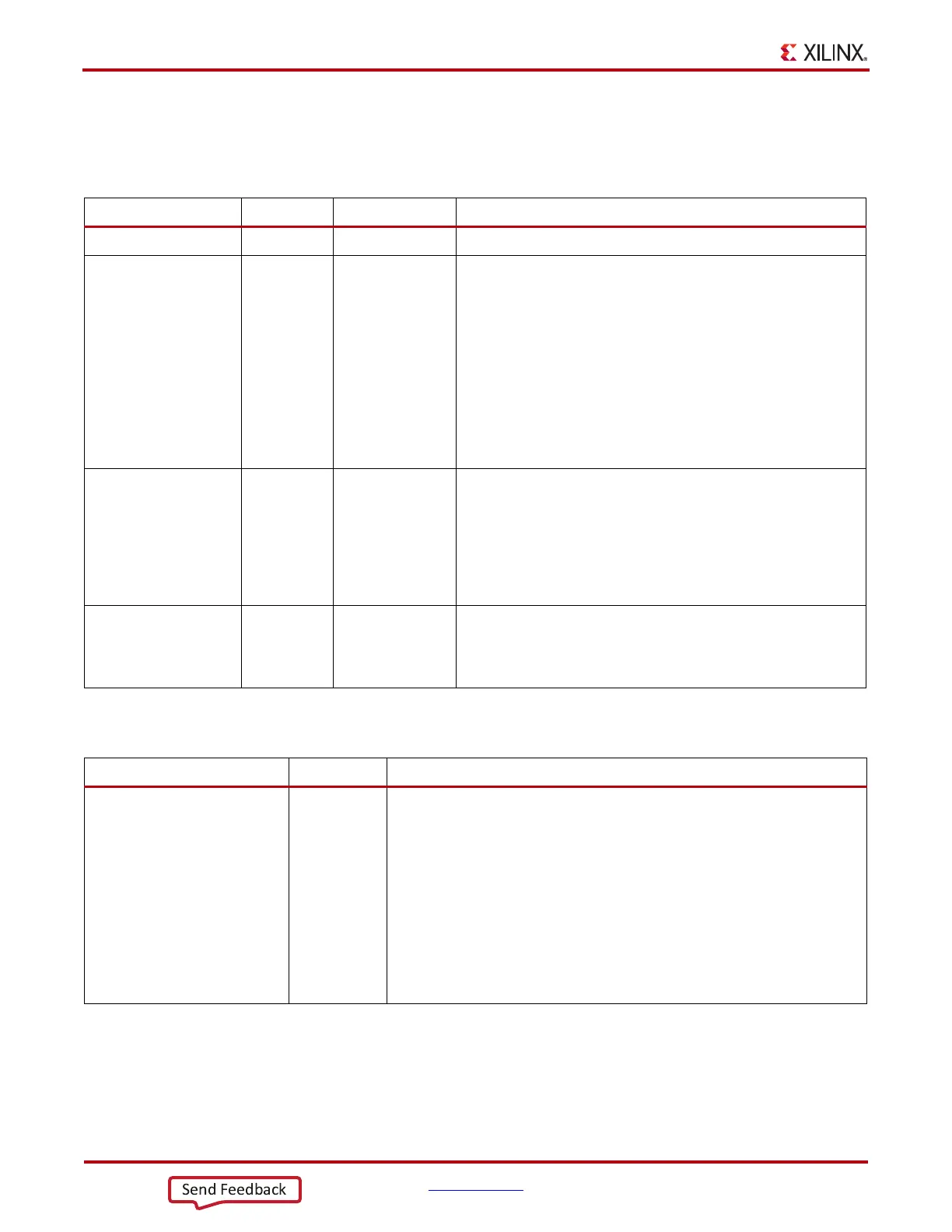

Table 4-36: RX Clock Correction Ports

Port Dir Clock Domain Description

RXBUFRESET In Async Resets the RX elastic buffer and related logic.

RXBUFSTATUS[2:0] Out RXUSRCLK2 Indicates the status of the RX elastic buffer:

000: In nominal operating range where the buffer occupancy is

within the CLK_COR_MIN_LAT and CLK_COR_MAX_LAT

range

001: RX elastic buffer occupancy is less than

CLK_COR_MIN_LAT

010: RX elastic buffer occupancy is greater than

CLK_COR_MAX_LAT

101: RX elastic buffer underflow

110: RX elastic buffer overflow

RXCLKCORCNT[1:0] Out RXUSRCLK2 Reports the clock correction status of the RX elastic buffer when the

first byte of a clock correction sequence is shown in RXDATA.

00: No clock correction

01: One sequence skipped

10: Two sequences skipped

11: One sequence added

RX8B10BEN In RXUSRCLK2 Active High to enable the 8B/10B decoder in the GTP transceiver

RX. If 8B/10B decoding is enabled, RX_DATA_WIDTH must be a

multiple of 10 (20, 40). If 8B/10B decoding is not enabled,

RX_DATA_WIDTH must be a multiple of 8 (16, 32).

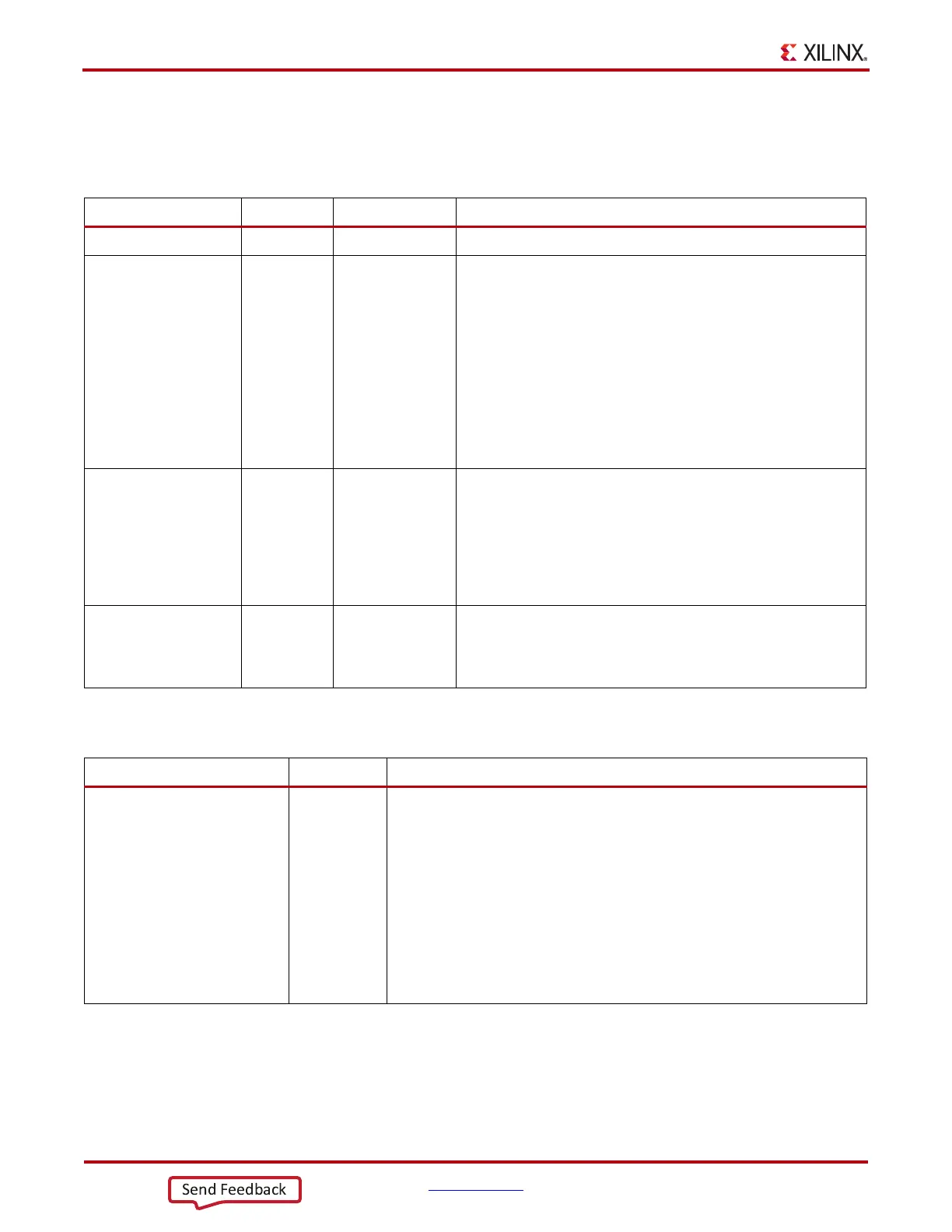

Table 4-37: RX Clock Correction Attributes

Attribute Type Description

CBCC_DATA_SOURCE_SEL String This attribute is used together with RX8B10BEN to select the data source for

clock correction and channel bonding.

When RX8B10BEN is High, CBCC_DATA_SOURCE_SEL = DECODED, the

clock correction sequence matches the data decoded after the 8B/10B decoder.

CBCC_DATA_SOURCE_SEL = ENCODED, the clock correction sequence

matches the raw data from the comma detection and realignment block before

the 8B/10B decoder.

When RX8B10BEN is Low, CBCC_DATA_SOURCE_SEL = DECODED is

not supported. CBCC_DATA_SOURCE_SEL = ENCODED, the clock

correction sequence matches the raw data from the comma detection and

realignment block.

Loading...

Loading...