7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 219

UG482 (v1.9) December 19, 2016

Pin Description and Design Guidelines

Termination Resistor Calibration Circuit

There is one resistor calibration circuit (RCAL) for each GTP Quad. The MGTRREF pin is used to

connect the bias circuit power and the external calibration resistor to the RCAL circuit. The RCAL

circuit performs the resistor calibration only during configuration of the FPGA. Prior to

configuration all analog supply voltages must be present and within the proper tolerance as specified

in DS181

, Artix-7 FPGAs Data Sheet: DC and Switching Characteristics.

The MGTRREF pin should be connected to the MGTAVTT supply through a 100Ω precision

external resistor. The resistor calibration circuit provides a controlled current load to the resistor that

is connected to the MGTRREF pin. It then senses the voltage drop across the external calibration

resistor and uses that value to adjust the internal resistor calibration setting. The quality of the

resistor calibration is dependent on the accuracy of the voltage measurement at the MGTRREF pin.

Managing Unused GTP Transceivers

In many applications only a portion of the GTP Transceivers are required. There are considerations

for managing the unused GTP Transceivers that affect such things as power consumption of the

Artix-7 FPGA. When considering which GTP Quads to use in an application, the organization of the

package power planes should be taken into account. Having multiple analog power planes in the

package allows for efficient utilization of power. If only a small portion of the GTP Quads will be

used then it might be possible to leave some of the GTP Quads completely un-powered.

Analog Power Supply Pins

The Artix-7 FPGA GTP Quad analog power supplies, MGTAVCC and MGTAVTT, have planes

inside the package. For some of the packages, there are multiple planes for each of these analog

power supplies. These planes are organized into groups with group designators such as G10 and

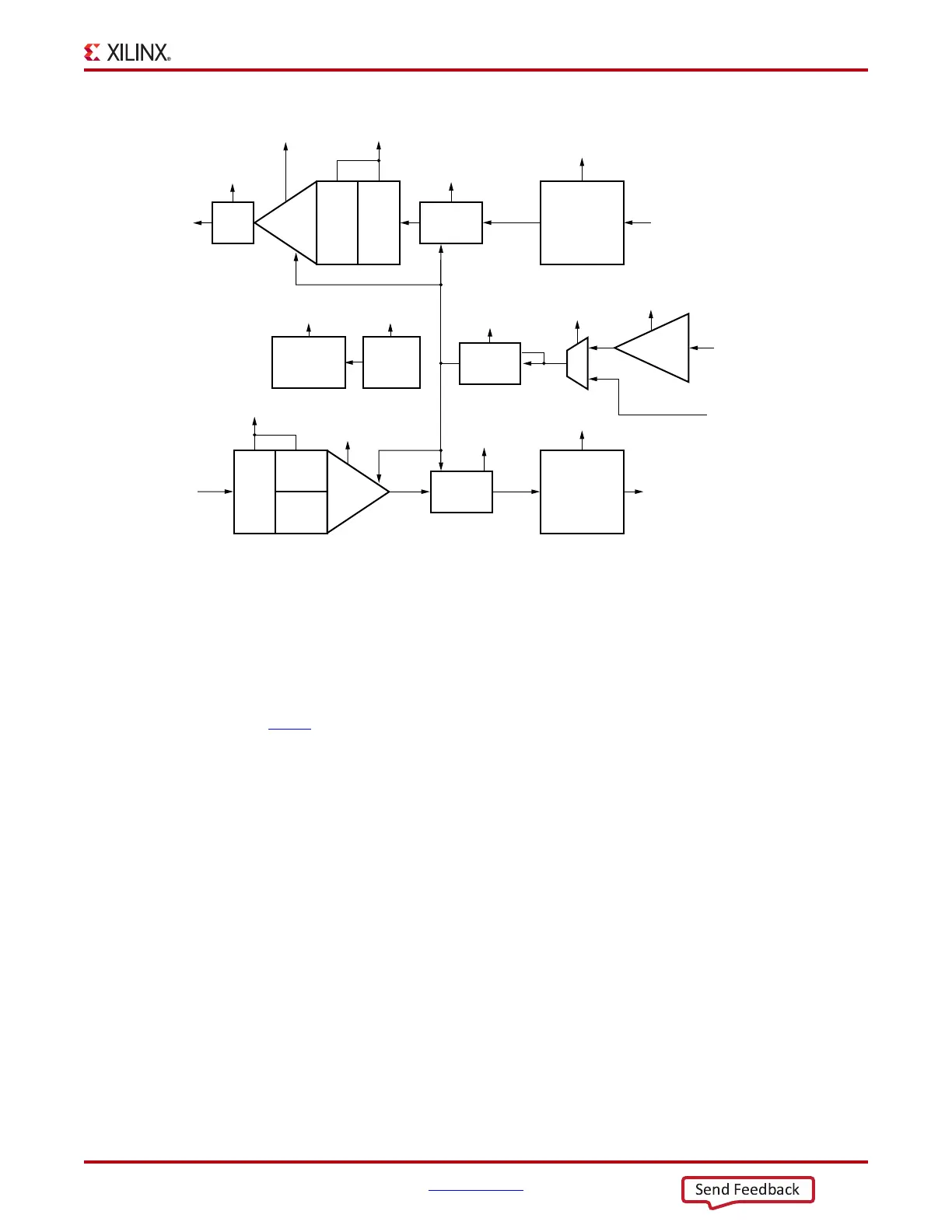

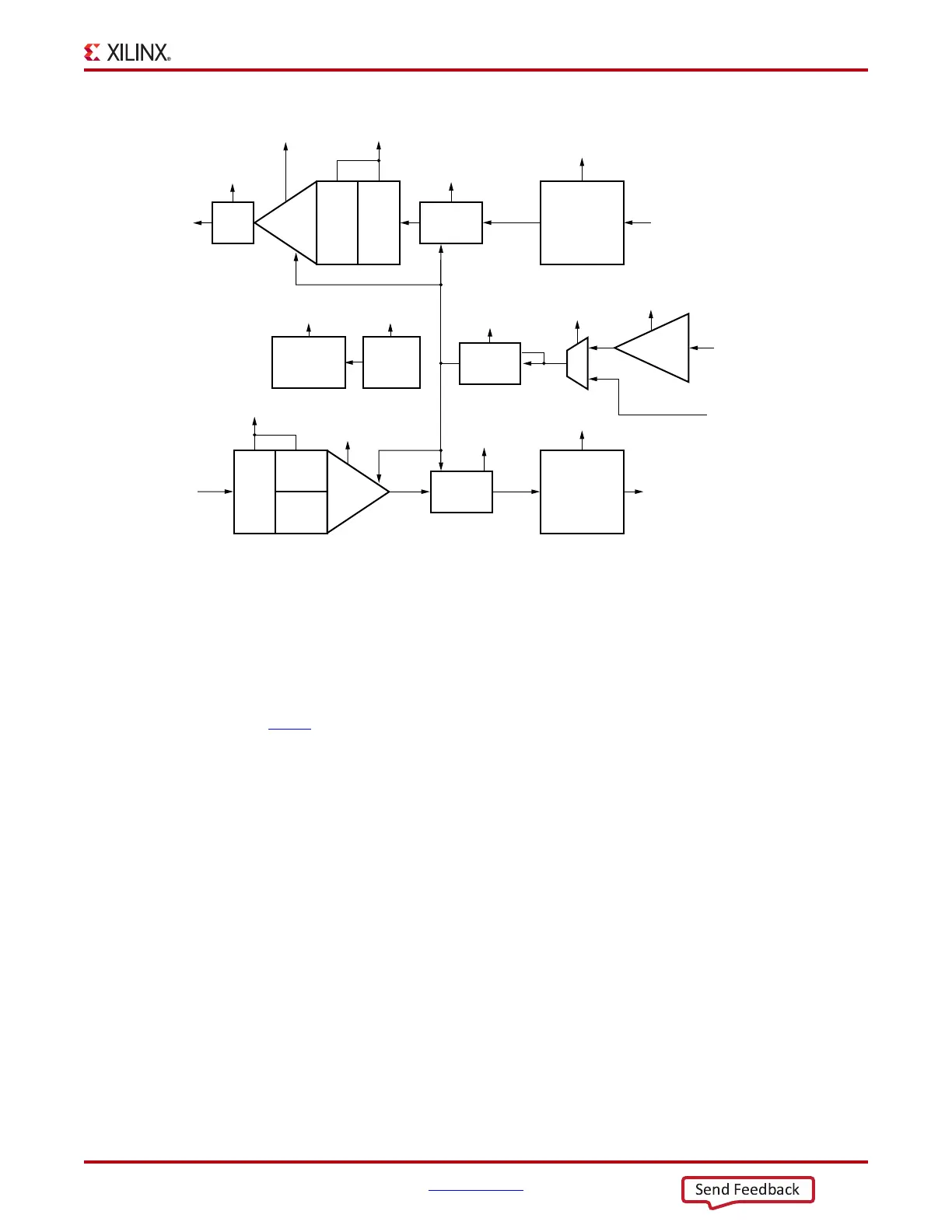

X-Ref Target - Figure 5-2

Figure 5-2: 7 Series FPGAs GTP Transceiver Internal Power Supply Connections

Tx

OOB

and

PCIe

PISO

MGTAVCC

MGTAVTT

PLL[0/1]

RefClk

Buffer

RX

EQ

MGTAVCC

MGTAVTT

MGTAVCC

TX

Term.

MGTAVTT

TX

Out

RX

In

MGTAVCC

Tx PCS

Rx PCS

Rx Fabric

Data In

VCCINT

VCCINT

External

RefClkInput

MGTAVTT

RCAL

MGTAVTT

RRCAL

InterQuad

Distribution

SIPO

MGTAVCC

TX

Driver

RX

CDR

MGTAVCC

UG482_c5_02_021113

MGTAVCC

Input

Term.

Tx

Pre/

Post

Emp

RX

OOB

Tx Fabric

Data Out

RefClocks

From Other

Quads

Loading...

Loading...