7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 29

UG482 (v1.9) December 19, 2016

Reference Clock Selection and Distribution

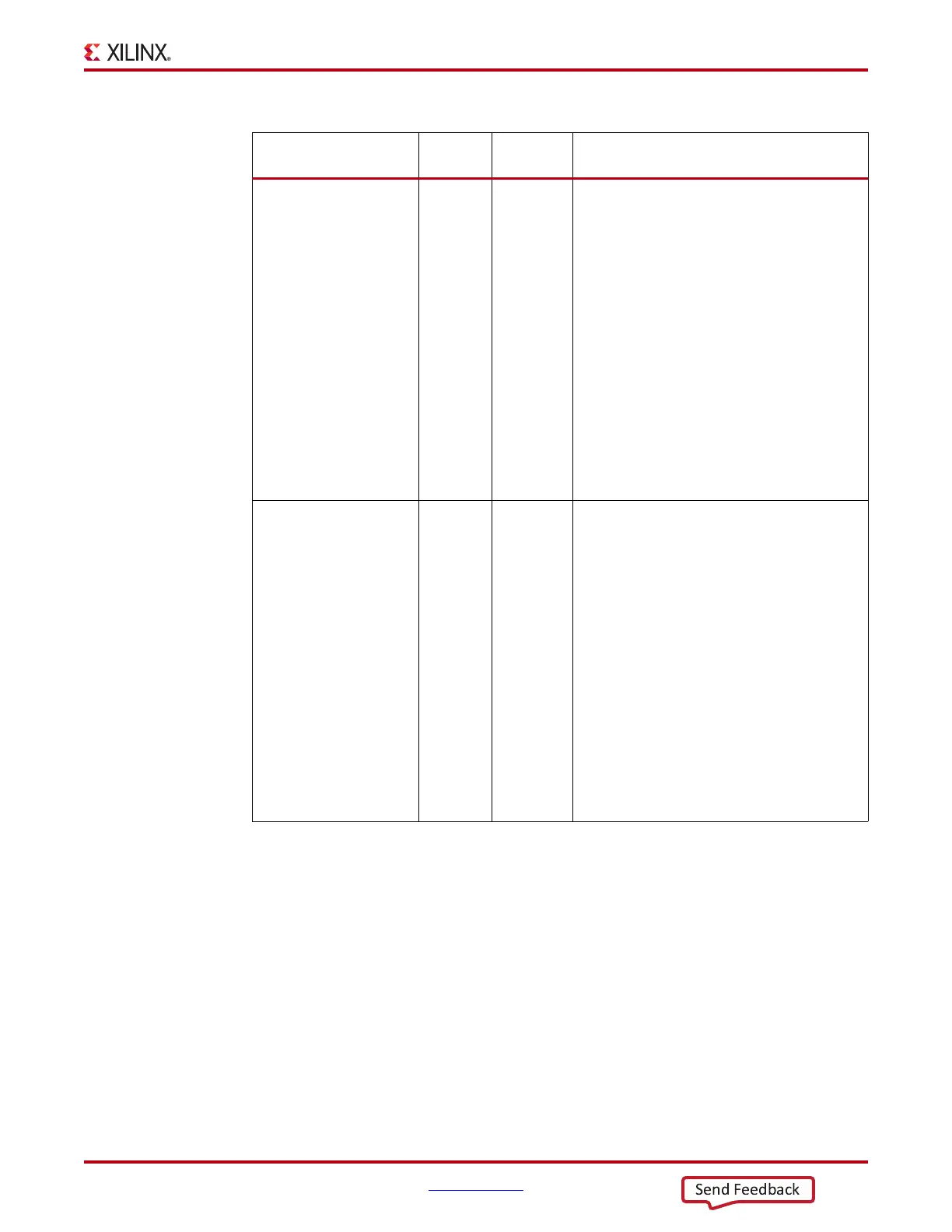

PLL0REFCLKSEL[2:0] In Async Input to dynamically select the input reference

clock to PLL0. This input should be set to

3'b001 when only one clock source is

connected to the PLL0 reference clock selection

multiplexer.

Reset must be applied to PLL0 after changing

the reference clock input.

000: Reserved

001: GTREFCLK0 selected

010: GTREFCLK1 selected

011: GTEASTREFCLK0 selected

100: GTEASTREFCLK1 selected

101: GTWESTREFCLK0 selected

110: GTWESTREFCLK1 selected

111: GTGREFCLK0 selected

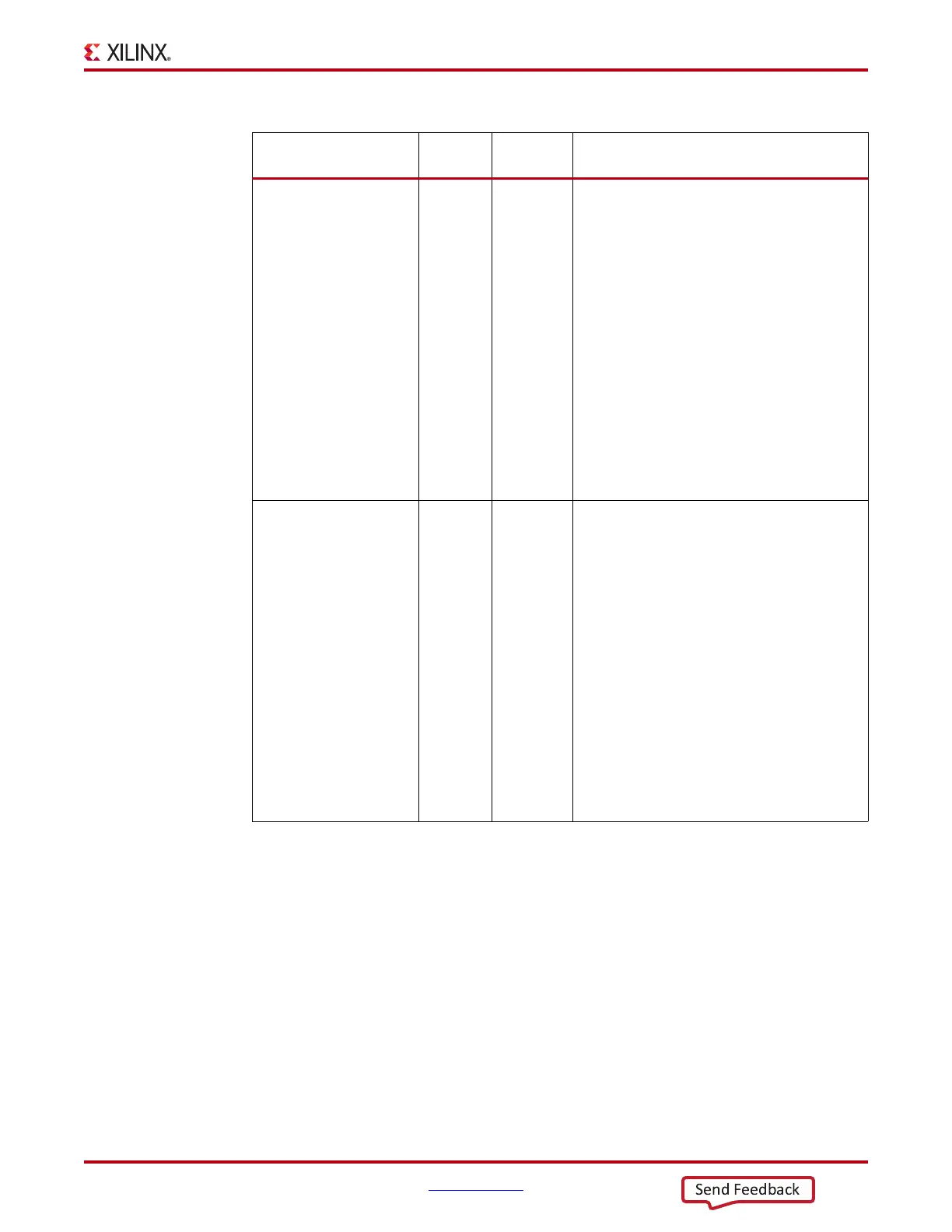

PLL1REFCLKSEL[2:0] In Async Input to dynamically select the input reference

clock to PLL1. This input should be set to

3'b001 when only one clock source is

connected to the PLL1 reference clock selection

multiplexer.

Reset must be applied to PLL1 after changing

the reference clock input.

000: Reserved

001: GTREFCLK0 selected

010: GTREFCLK1 selected

011: GTEASTREFCLK0 selected

100: GTEASTREFCLK1 selected

101: GTWESTREFCLK0 selected

110: GTWESTREFCLK1 selected

111: GTGREFCLK1 selected

Table 2-4: GTPE2_COMMON Clocking Ports (Cont’d)

Port Direction

Clock

Domain

Description

Loading...

Loading...