30 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 2: Shared Features

Table 2-6 defines the clocking ports for the GTPE2_CHANNEL primitive.

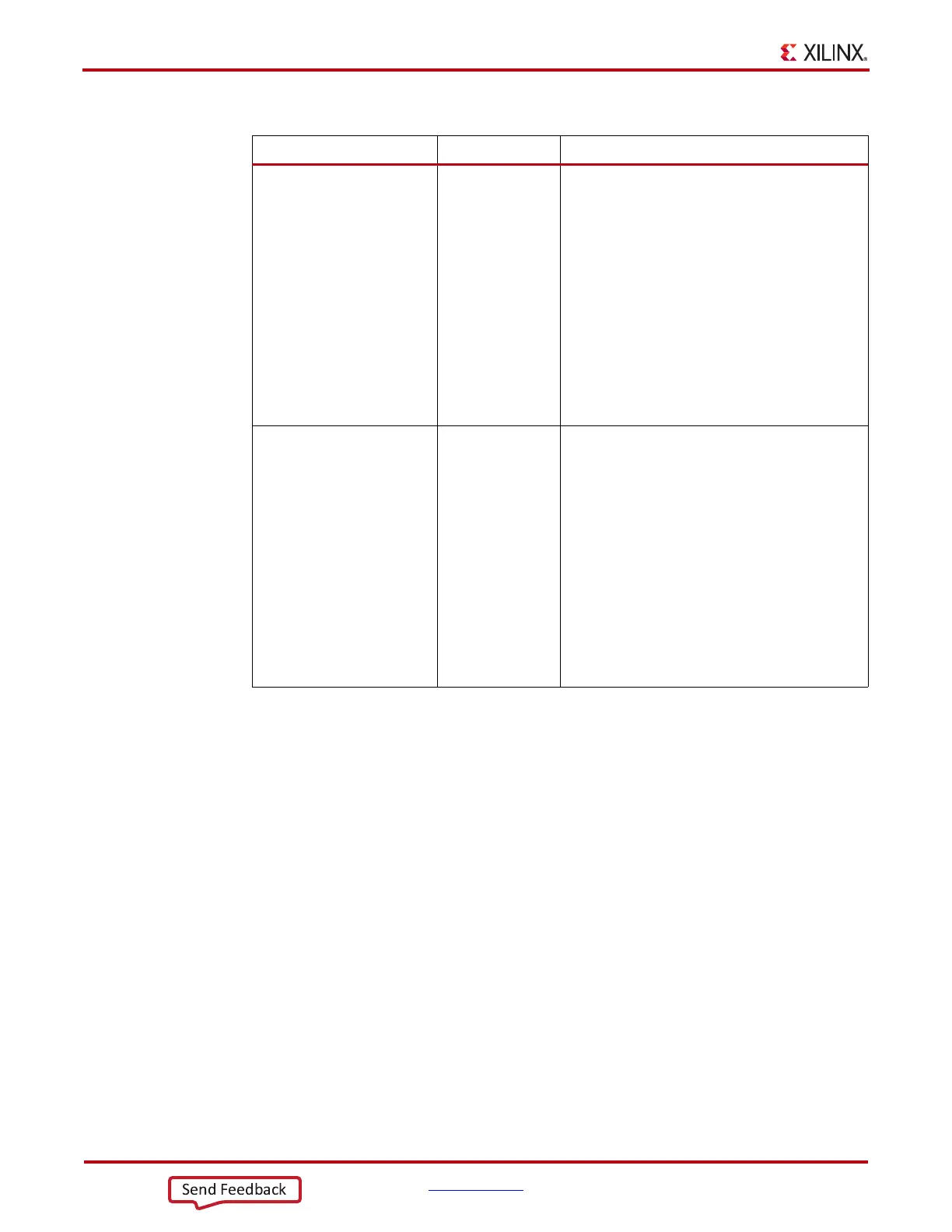

Table 2-5: GTPE2_COMMON Attributes

Attribute Type Description

SIM_PLL0REFCLK_SEL 3-bit Binary This attribute selects the reference clock source

used to drive PLL0 in simulation for designs

where PLL0 is always driven by the same

reference clock source.

SIM_PLL0REFCLK_SEL allows for simulation

before and after the port swap changes. This

allows for the block to be simulated with the

correct clock source both before and after the port

swap. SIM_PLL0REFCLK_SEL must be set to

the same value as PLL0REFCLK SEL[2:0]. For

designs that require the reference clock source to

be changed on the fly, the port PLL0REFCLKSEL

is used instead to dynamically select the reference

clock source.

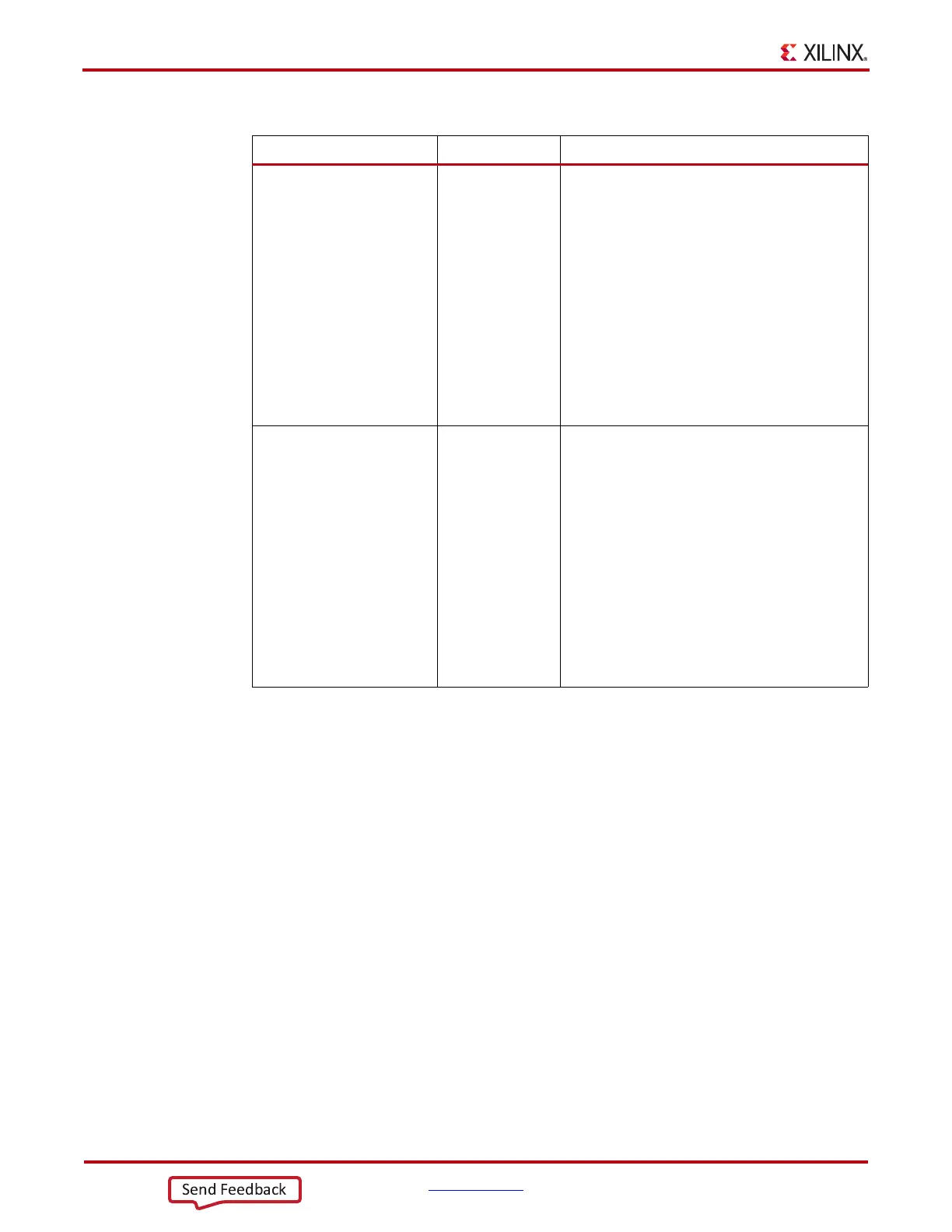

SIM_PLL1REFCLK_SEL 3-bit Binary This attribute selects the reference clock source

used to drive PLL1 in simulation for designs

where PLL1 is always driven by the same

reference clock source.

SIM_PLL1REFCLK_SEL allows for simulation

before and after the port swap changes. This

allows for the block to be simulated with the

correct clock source both before and after the port

swap. SIM_PLL1REFCLK_SEL must be set to

the same value as PLL1REFCLK SEL[2:0]. For

designs that require the reference clock source to

be changed on the fly, the port PLL1REFCLKSEL

is used instead to dynamically select the reference

clock source.

Loading...

Loading...