108 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 4: Physical Interface

R

hold times of the input GMII receiver signals which are sampled at the GMII IOB input

flip-flops.

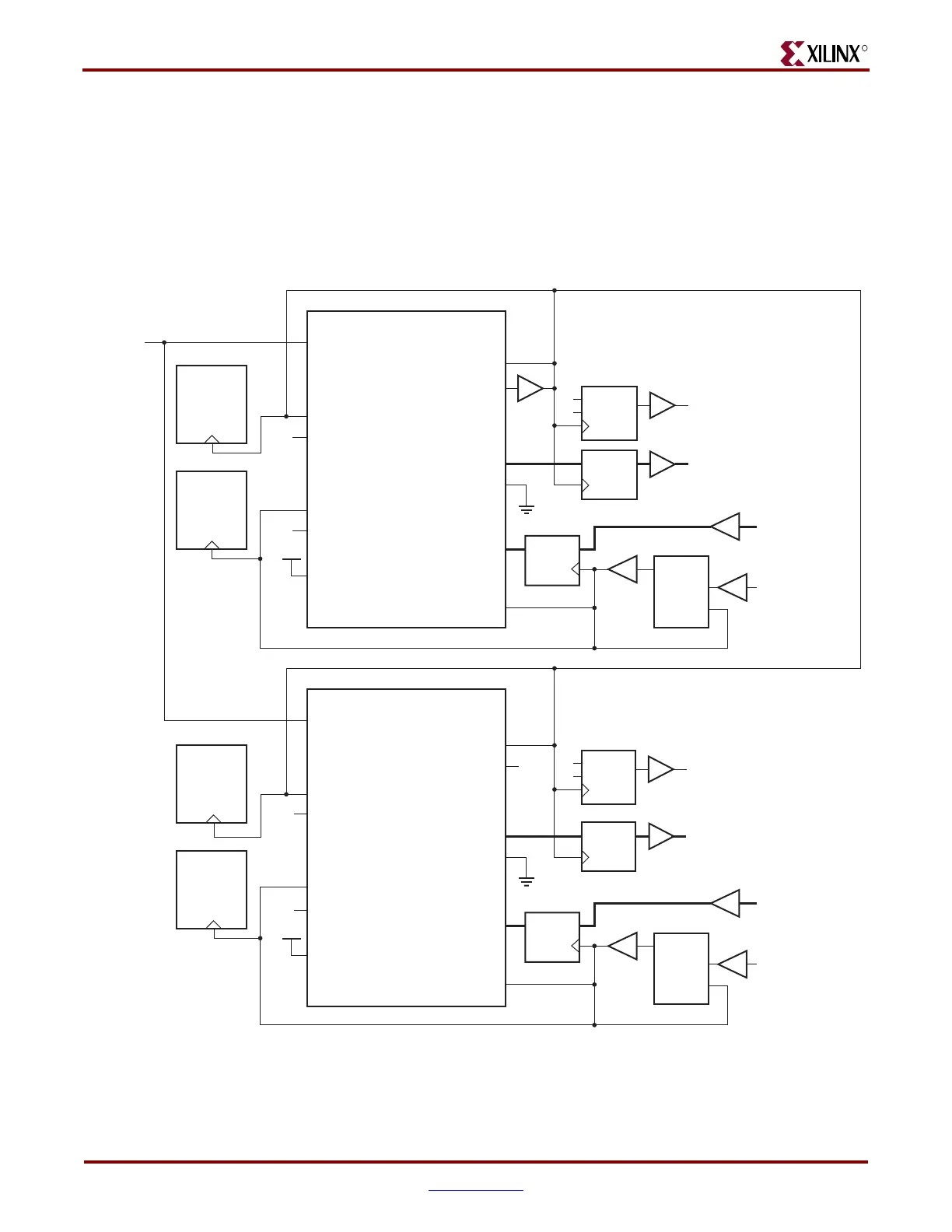

Figure 4-8 shows the GMII clocking scheme with two Ethernet MACs enabled. It is similar

to the single Ethernet MAC clocking scheme, however, one of the

EMAC#CLIENTTXGMIIMIICLKOUT signals is used for all (both Ethernet MACs)

transmitter logic.

Figure 4-8: 1 Gb/s GMII Clock Management with Two Ethernet MACs Enabled

EMAC1CLIENTTXGMIIMIICLKOUT

CLIENTEMAC1TXGMIIMIICLKIN

PHYEMAC1GTXCLK

CLIENTEMAC1TXCLIENTCLKIN

EMAC1CLIENTTXCLIENTCLKOUT

CLIENTEMAC1RXCLIENTCLKIN

EMAC1CLIENTRXCLIENTCLKOUT

PHYEMAC1TXD[7:0]

PHYEMAC0MIITXCLK

EMAC1

TX CLIENT

LOGIC

RX CLIENT

LOGIC

OBUF

GMII_TXD_1[7:0]

Q

D

GND

NC

NC

EMAC0CLIENTTXGMIIMIICLKOUT

CLIENTEMAC0TXGMIIMIICLKIN

PHYEMAC0GTXCLK

CLIENTEMAC0TXCLIENTCLKIN

EMAC0CLIENTTXCLIENTCLKOUT

CLIENTEMAC0RXCLIENTCLKIN

EMAC0CLIENTRXCLIENTCLKOUT

PHYEMAC0RXCLK

PHYEMAC0TXD[7:0]

PHYEMAC0RXD[7:0]

PHYEMAC0MIITXCLK

EMAC0

GTX_CLK

TX CLIENT

LOGIC

RX CLIENT

LOGIC

BUFG

OBUF

GMII_TXD_0[7:0]

QD

GND

NC

NC

NC

UG074_3_54_040609

OBUF

GMII_TX_CLK_0

Q

D1

D2

ODDR

0

1

OBUF

GMII_TX_CLK_1

Q

D1

D2

ODDR

0

1

CLIENTEMAC1DCMLOCKED

CLIENTEMAC0DCMLOCKED

PHYEMAC1RXCLK

PHYEMAC1RXD[7:0]

GMII_RXD_#[7:0]

GMII_RX_CLK_#

IBUF

IBUFG

BUFG

QD

CLK0

CLKIN

CLKFB

DCM

GMII_RXD_#[7:0]

GMII_RX_CLK_#

IBUF

IBUFG

BUFG

QD

CLK0

CLKIN

CLKFB

DCM

Loading...

Loading...