24 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 2: Ethernet MAC Architecture

R

Flow Control Client-Side Interface Signals

Table 2-3 describes the signals used by the client to request a flow control action from the

transmit engine. The flow control block is designed per the specifications in Clause 31 of

the IEEE Std 802.3-2002 standard. Flow control frames received by the Ethernet MAC are

automatically handled.

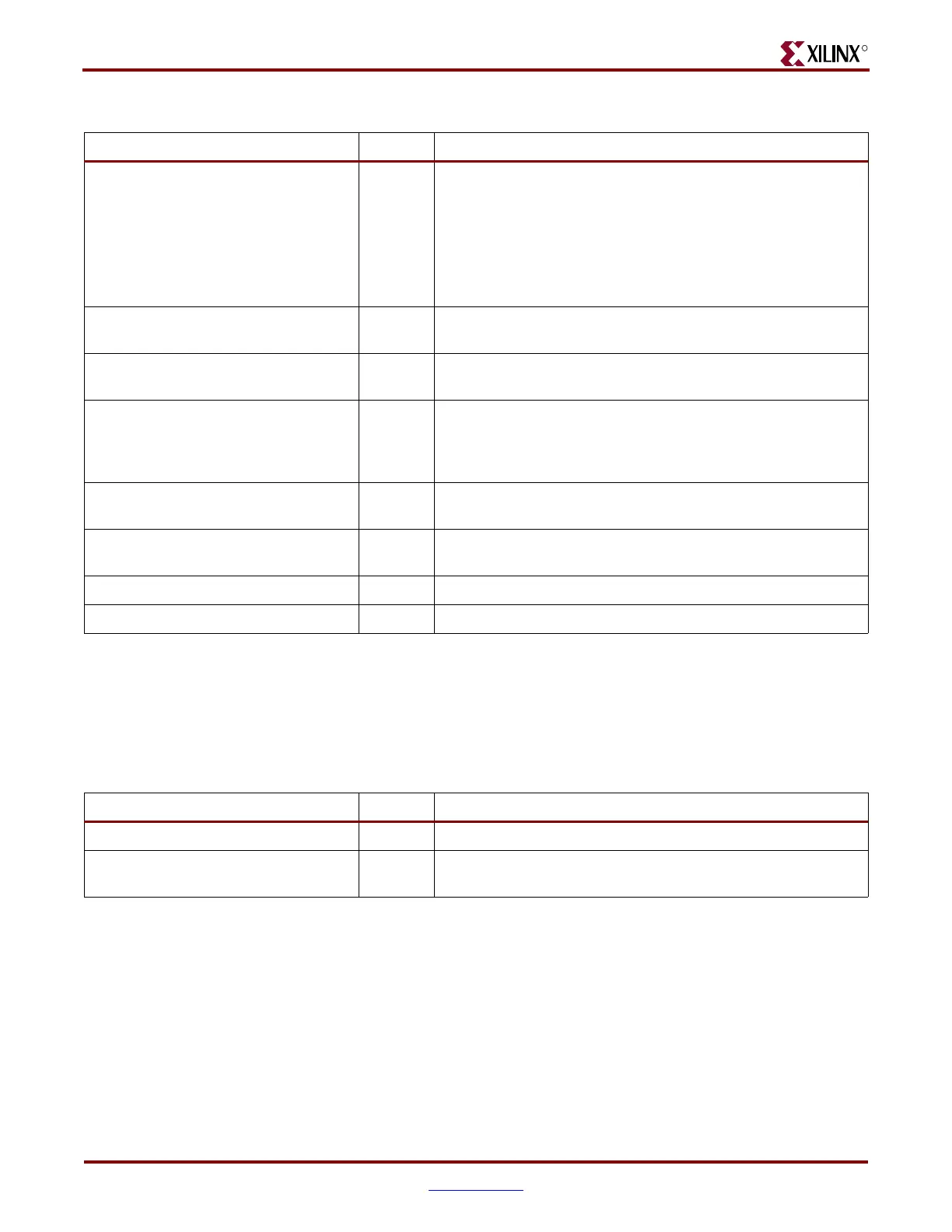

EMAC#CLIENTRXDVLDMSW Output

This signal denotes an odd number of bytes in the receive data

path when the width of EMAC#CLIENTRXD is set to 16 bits

wide.

In a frame with an odd number of bytes, the

EMAC#CLIENTRXD[7:0] byte is valid on the last byte.

When the width of EMAC#CLIENTRXD is set to 8 bits wide, this

signal should be left unconnected.

EMAC#CLIENTRXGOODFRAME Output

This signal is asserted after the last receipt of data to indicate the

reception of a compliant frame.

EMAC#CLIENTRXBADFRAME Output

This signal is asserted after the last receipt of data to indicate the

reception of a non-compliant frame.

EMAC#CLIENTRXSTATS[6:0] Output

The statistics data on the last received data frame. The 27-bit raw

RX statistics vector is multiplexed into a seven-bits per RX clock

cycle output for statistics gathering. See “Receiver Statistics

Vector” in Chapter 3.

EMAC#CLIENTRXSTATSBYTEVLD Output

Asserted if an Ethernet MAC frame byte (including destination

address to FCS) is received. Valid on every RX clock cycle.

EMAC#CLIENTRXSTATSVLD Output

Asserted by the Ethernet MAC after the end of receiving a frame

to indicate a valid EMAC#CLIENTRXSTATS[6:0] output.

EMAC#CLIENTRXCLIENTCLKOUT Output See “Receive Clocking Scheme” in Chapter 5.

EMAC#CLIENTRXDVREG6 Output Reserved - not used.

Table 2-2: Receive Client Interface Signals (Cont’d)

Signal Direction Description

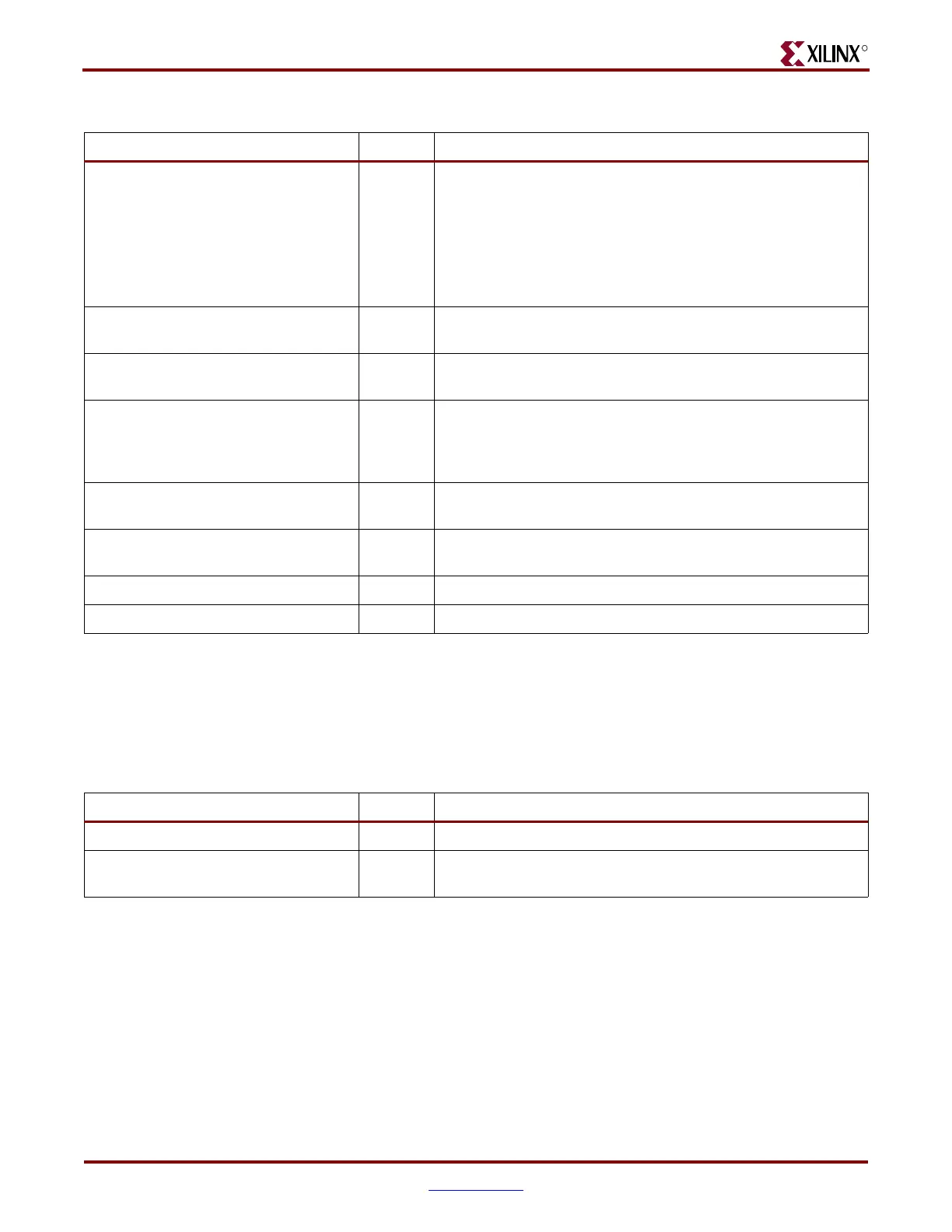

Table 2-3: Flow Control Interface Signals

Signal Direction Description

CLIENTEMAC#PAUSEREQ Input Asserted by client to transmit a pause frame.

CLIENTEMAC#PAUSEVAL[15:0] Input

The amount of pause time for the transmitter as defined in the

IEEE Std 802.3-2002 specification.

Loading...

Loading...