70 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 3: Client, Host, and MDIO Interfaces

R

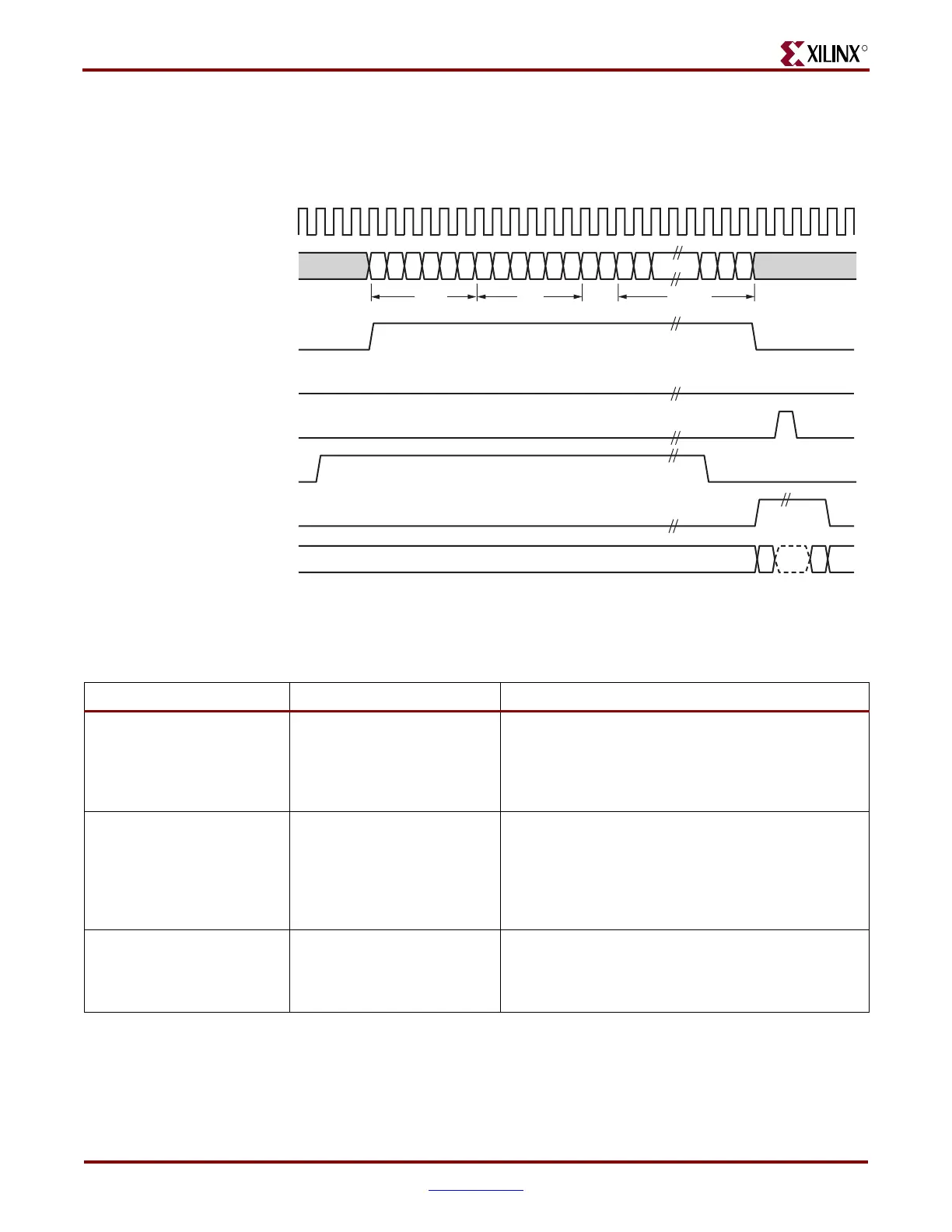

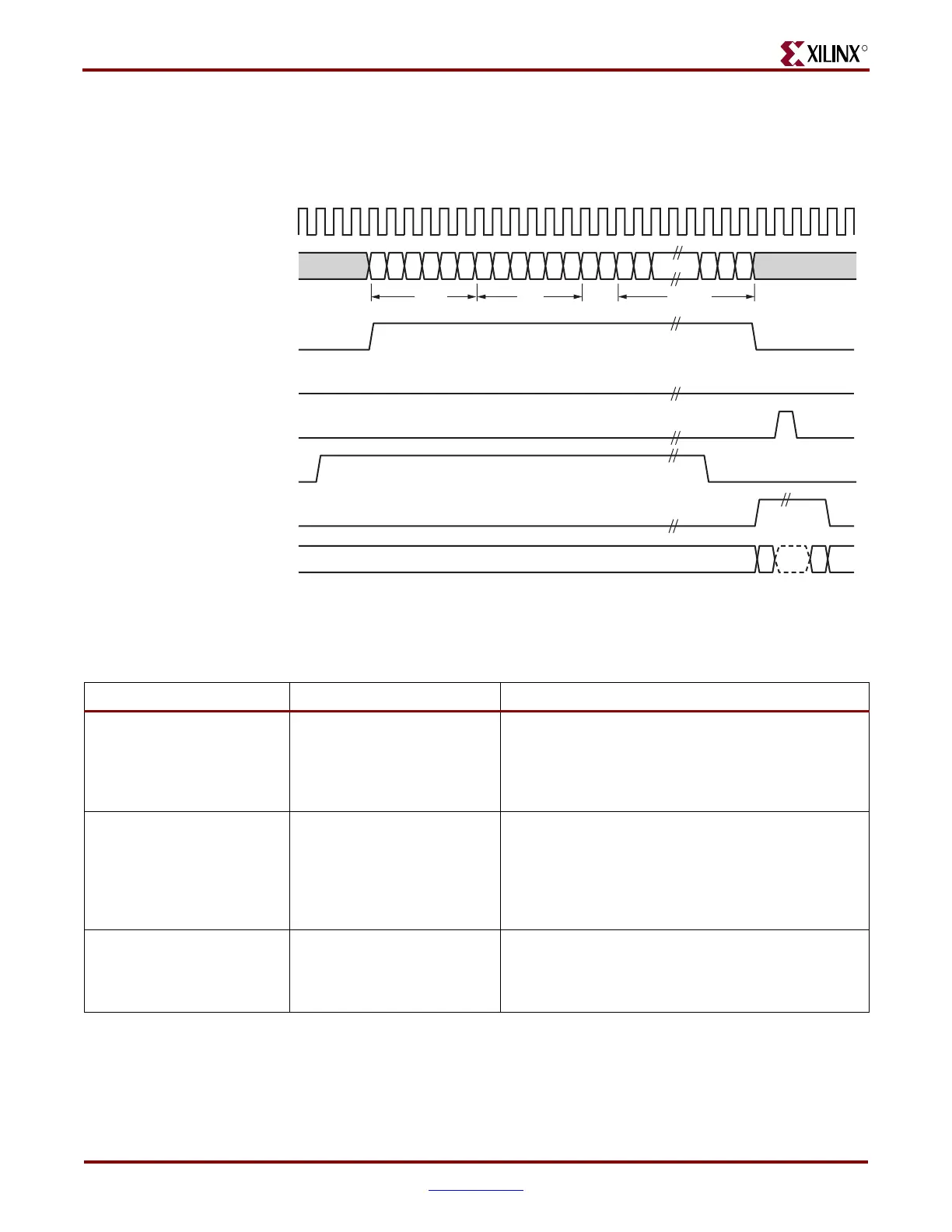

All bit fields for the EMAC#CLIENTRXSTATS[6:0] are valid only when the

EMAC#CLIENTRXSTATSVLD is asserted as illustrated in Figure 3-37.

EMAC#CLIENTRXSTATSBYTEVLD is asserted if an Ethernet MAC frame byte (DA to

FCS inclusive) is received. This is valid on every CLIENTEMAC#RXCLIENTCLKIN cycle.

Figure 3-37: Receiver Statistics Vector Timing

DA SA DATAL/T

ug074_3_39_010906

[6:0] [26:21]

EMAC#CLIENTRXDVLD

EMAC#CLIENTRXDVLDMSW

EMAC#CLIENTRXGOODFRAME

EMAC#CLIENTRXSTATSBYTEVLD

EMAC#CLIENTRXSTATS[6:0]

EMAC#CLIENTRXSTATSVLD

EMAC#CLIENTRXD[7:0]

CLIENTEMAC#RXCLIENTCLKIN

Table 3-5: Bit Definitions for the Receiver Statistics Vector

RX_STATISTICS_VECTOR Name Description

26 ALIGNMENT_ERROR

Used in 10/100 MII mode. If an odd number of nibbles

is received, the last nibble is ignored. If the frame

without this nibble has an incorrect FCS, this bit is

asserted. If the frame has a valid FCS, this bit is not

asserted.

25 Length/Type Out of Range

Asserted if the LT field contains a length value that

does not match the number of Ethernet MAC client

data bytes received. Also asserted High if the LT field

indicates that the frame contains padding but the

number of Ethernet MAC client data bytes received is

not equal to 46 bytes (minimum frame size).

24 BAD_OPCODE

Asserted if the previous frame is error free, contains the

special control frame identifier in the LT field, but

contains an OPCODE unsupported by the Ethernet

MAC (any OPCODE other than PAUSE).

Loading...

Loading...