iSeries architecture: Fundamental strength of the IBM ^ i5 and iSeries 13

Draft Document for Review October 18, 2004 5486AdvTech.fm

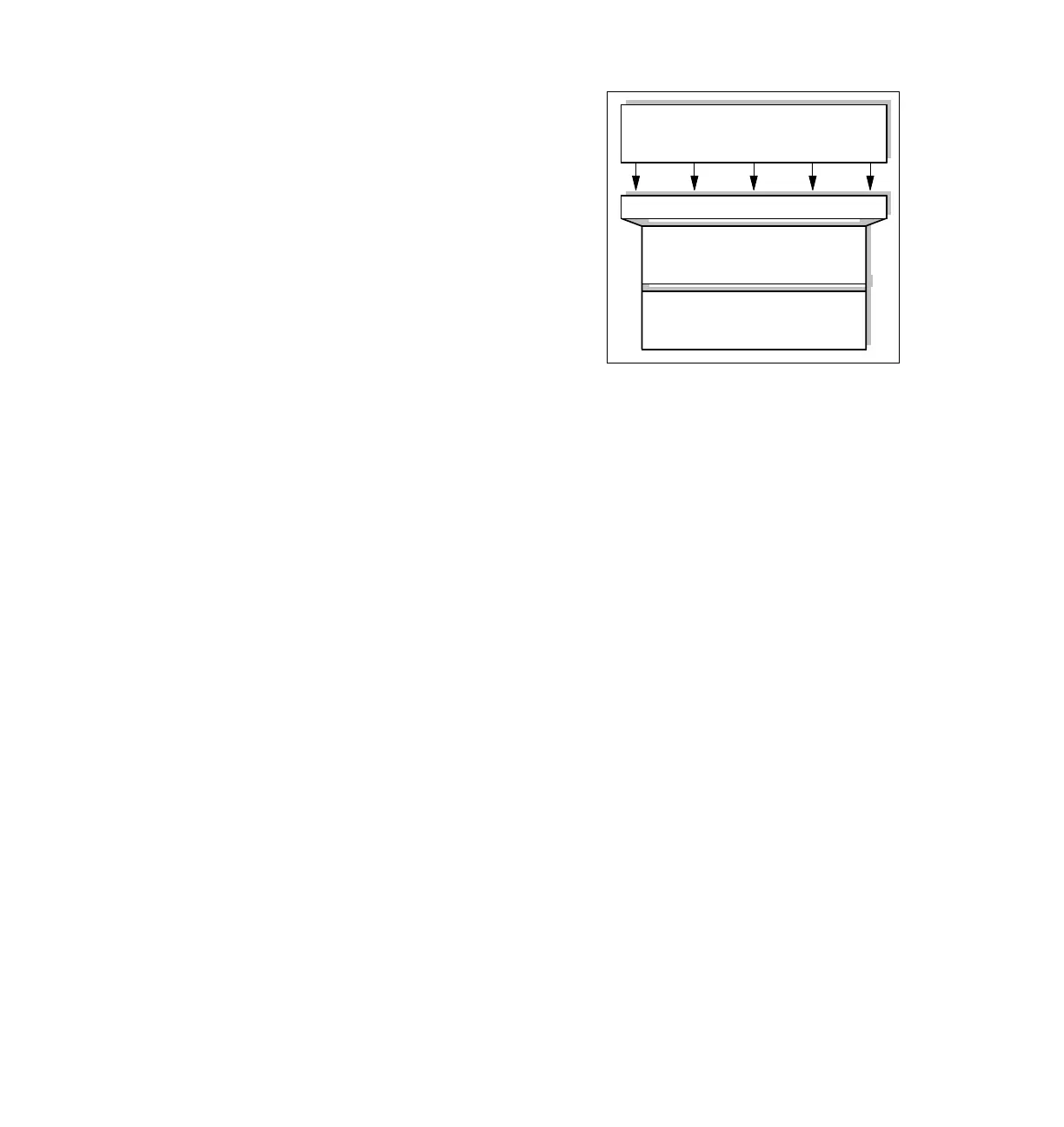

The microcode layer is known as the

System Licensed Internal Code. Many of

the frequently-executed routines run in

SLIC. Supervisory resource

management functions in SLIC include

validity and authorization checks. On a

customary system, these routines reside

in the operating system. Because SLIC

is closer to the silicon, routines

performed there are faster than routines

placed “higher” in the machine.

The brilliance of this design was

dramatically illustrated when the AS/400

system changed its processor technology from CISC processors to 64-bit RISC

processors in 1995. With any other system, the move from CISC to RISC would

involve recompiling (and possibly some rewriting) programs. Even then, with

other systems, the programs would run in 32-bit mode on the newer 64-bit

hardware.

This is not so with the iSeries server, because of TIMI. Customers were able to

save programs off their CISC AS/400 systems and restore them on their RISC

AS/400e™ models. The programs run as 64-bit programs. As soon as they made

this transition, customers had

64-bit application programs that ran on a 64-bit

operating system

, containing a 64-bit relational database that fully exploited the

64-bit RISC hardware.

TIMI and SLIC take technology in stride. New architectural features are exploited

to fully accommodate post-RISC technologies, which may incorporate 96-bit or

128-bit processors or shifts to different processor technologies. TIMI helps

condition the iSeries to bring new technology to market.

POWER Hypervisor

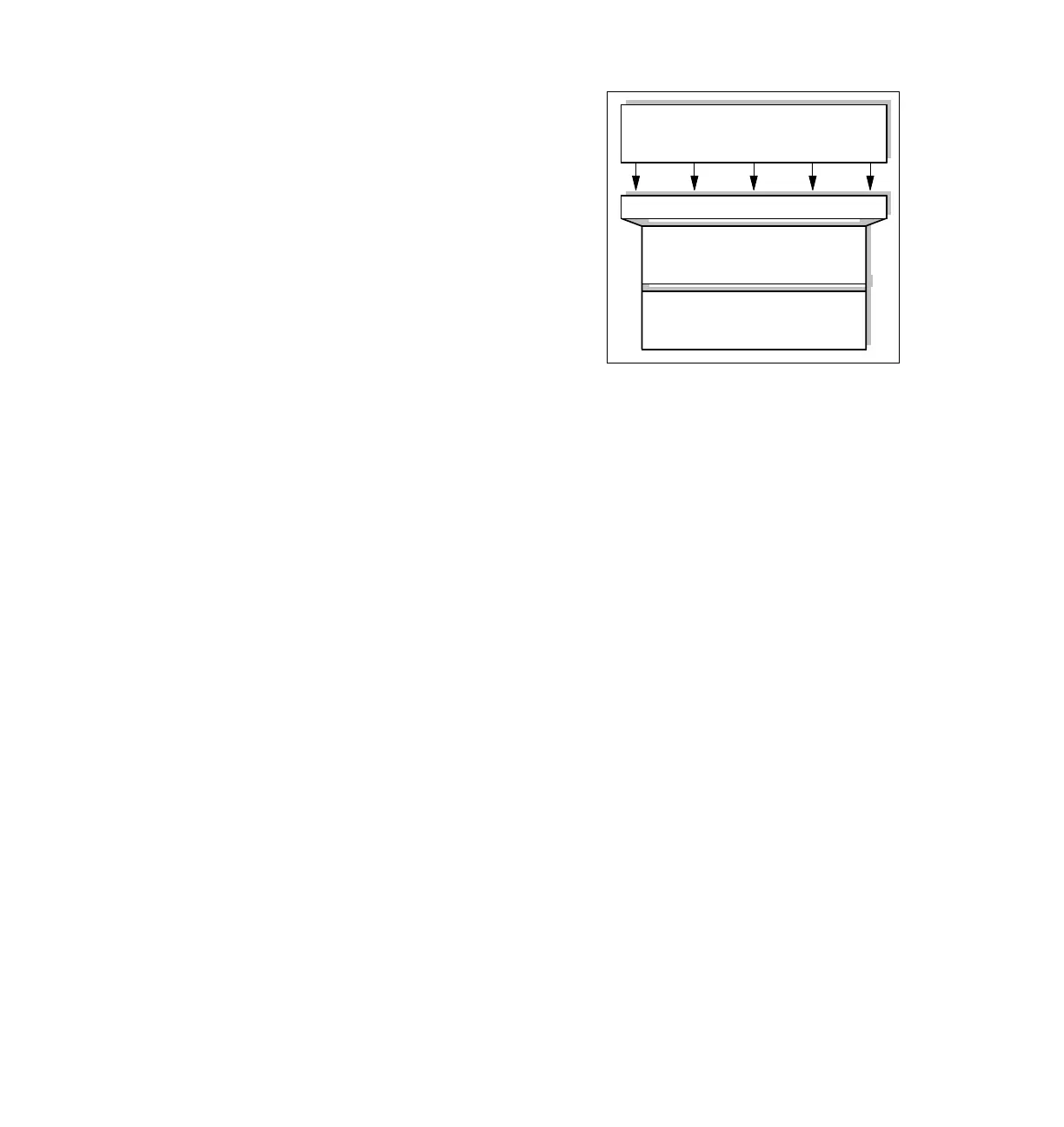

IBM Eserver i5 servers work with a different structure when compared to the

previous technologies used with the iSeries servers. Above the POWER5

technology-based hardware is a new code layer called the

POWER™

Hypervisor

.

This code is part of the firmware shipped with the Eserver i5 hardware. The

POWER Hypervisor resides in flash memory on the Service Processor. This

firmware performs the initialization and configuration of the Eserver i5

hardware, as well as the virtualization support required to run up to 254 partitions

concurrently on the Eserver i5 servers.

Programs

TIMI

SLIC

64-bit RISC Hardware

Loading...

Loading...