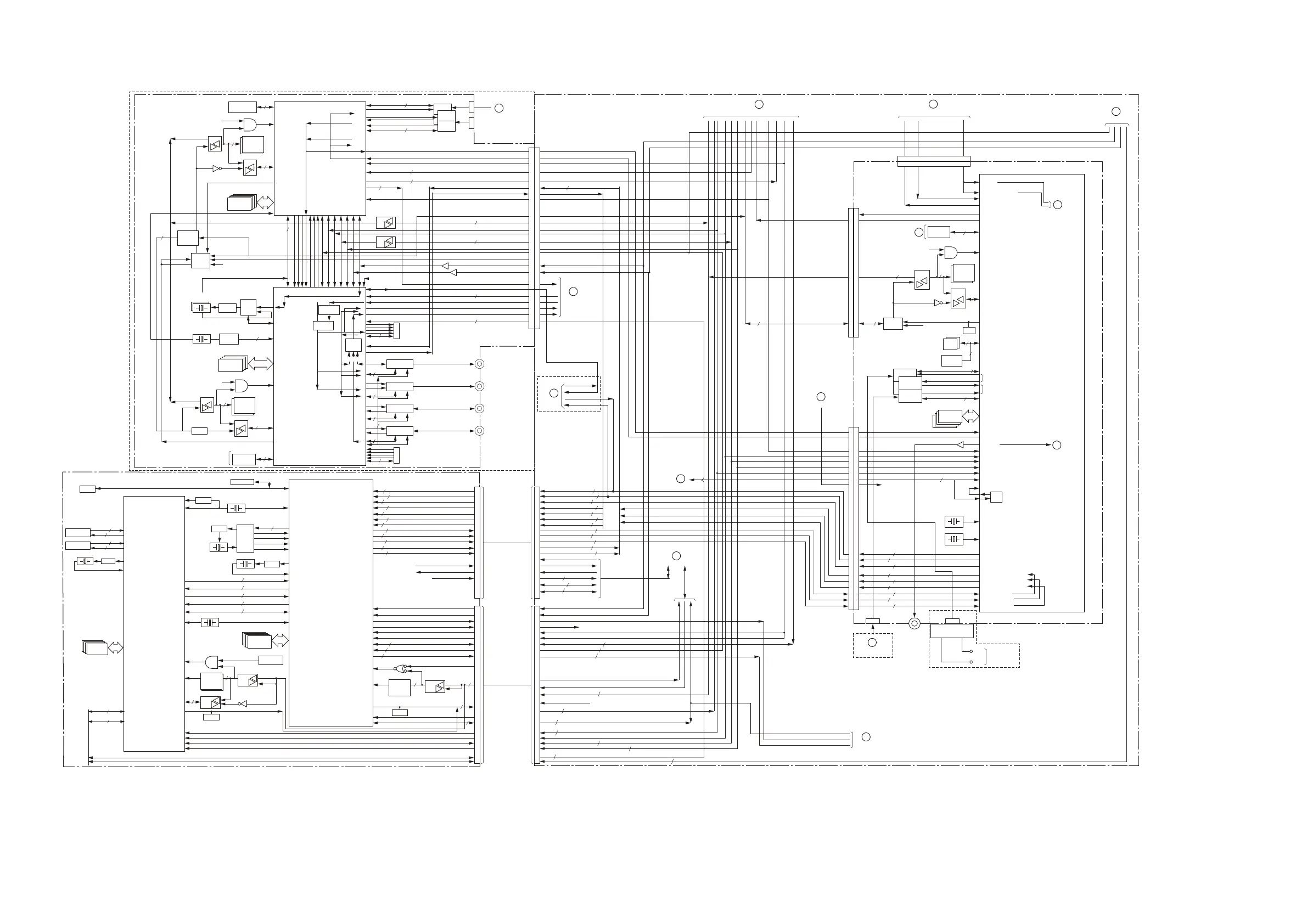

PLD_CONF_DONE(and INIT_DONE)

DRAM_I/F(16bit)

DRAM_I/F(16bit)

EXT_CONFIG(4)

VIF-MIF RESERVE(6)

256FS

64FS

LRCK(FS_48kHz)

DRAM_I/F(16bit)

DRAM_I/F(16bit)

PROGRAM_B

VUP_SPI(4)

AU_SY2VIF[2:0]

AU_VIF2SY[4:0]

IRQ

SFP_CTRL(6)

CLK_100

CLK_148.5

NET_RET_3G

NET_RET_4K1

NET_RET_4K2

NET_RET_THRU_3G

NET_RET_THRU_4K1

NET_RET_THRU_4K2

INT_AT[0]

NET_MAIN_3G

NET_MONI_3G

NET_HD_TRUNK

SFP_CTRL(6)

PLL

OPTICAL MODULE

100Hz

125Hz

FG-OUT

LASER_ON_DET

CPU_CLK

CPU_BUS(20)

CPU_CS

RESET_FPGA

MAIN

RET

I2C

LED

PLD_CONF_DONE

EPR2

JTAG_CN

PLD_VU_CS/ROM_SEL

PLD_RECONFIG

4

4

NCONF

SPIFlash

Config

ROM

E/O

O/E

IO

EXP

5

6

PCB_ID[3:0]

E/O

O/E

Te mp

Sens

EEPROM

6

148.5MHz(Fix)

VC1202

CN403 J6000

F-GATE

OUT

CAMERA SMF

HKCU-SM50

IN

OUT

XRST

6

PCI Express

PWRUNIT_PG

4

2

2

2 2

2

4

6

4

6

8

3

2

2

20

3

3

MAIN 3G

3G_SDI 4K

3G_SDI 4K

3G_SDI 4K

3G_SDI 4K

MONI 3G

HD_TRUNK

NET_RET_4K1

NET_RET_4K2

NET_RET_3G

NET_RET_4K3

NET_RET_4K4

PWR_GOOD_SLOT

PWR_EN_SLOT

PCB_ID

I2C_12G

OP_SPI

EEPROM_WP

NET_CLK_74

MST_CLK_27

MST_CLK_74

MST_CLK_27

MST_CLK_74

NET_CLK_27

CN404

2

2

2

2

2

2

2

2

2

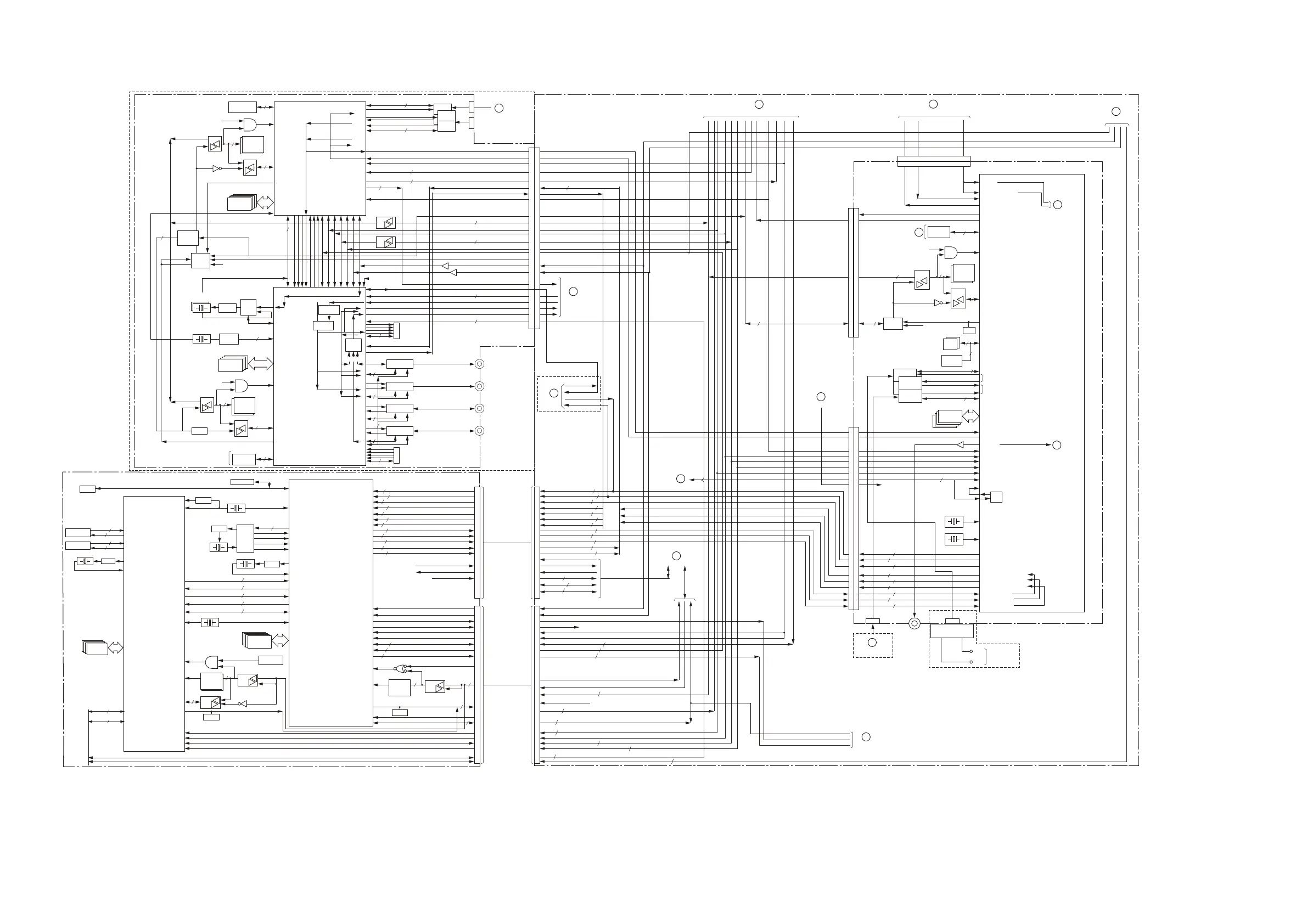

DDR4

SDRAM

E/O

O/E

DDR4

SDRAM

DDR4

4Gbit

SYNC(F/V/H/FG)

VIF-75 (1/2)

MB-1257 (3/5)

IC1700 (1/2)

TX-167B

NET-37

TX (FPGA)

4K-POST (FPGA)

FPGA

FPGA

NET_RET

NET_MAIN 4K

XRST

SLOT_ID[2:0]

MST_CLK_74

MST_CLK_27

I2C

256FS, LRCK

META/GATE/CAM-CHARA

RET 1/2/3(HD_Prompter)

MAIN HD1/2,HD-TRUNK1/2

MAIN for UPCONV

META/CAM-CHARA/AUDIO

MAIN for 3G-SDI OUT

SUB for VIF

6GX4

PCI Express

NET_RET

NET_MAIN 4K

EPR2

JTAG_CN

CN1101

IC601

CN201

CN202

IC002

CN0102 CN403

CN0101 CN402

IC1501

8

4

4

4

2

7

8

2x5

MAIN 3G

MONI 3G

2

2

HD_TRUNK

2

3G_SDI 4K

2

3G_SDI 4K

2

3G_SDI 4K

2

3G_SDI 4K

2

IP_RET1

2

IP_RET2

2

2

4

3

IP_HD-PROMPTER

PWR_GOOD_SLOT

PWR_EN_SLOT

PCB_ID[0]

I2C(SDA/SCL)(2)

DRAM_I/F(118)

CLK_100CLK_100

BUS_RSVBUS_RSV

NET_CLK_74

NET_CLK_27

256FS

LRCK(FS_48kHz)

AU_DATA(TX/RX)(2)

SYNC(F/V/H/F-Gate)

NET_REF(F/V/H)

2

IP_4K_RET_for4K

2

IP_HD_RET_for4K

2

2

2

2

2

2

2

2

2

2

2

2

2

2

3

3

3

3

5

6

6

6

2x2

7

8

SFP_CTRL(8)

SFP_CTRL(8)

RET

RET

256FS, LRCLK

AU_TX2SY[1:0]

META/GATE/CAM-CHARA

LASER_ON

4K MAIN

PCB_ID[3:0]

(UHD-TRUNK)

UHD Prompter (4K-RET)

700P_MAIN_TX/RX(2)

700P_SUB_TX/RX(2)

MAIN

NCONF

PLD_RECONFIG

PWR_GOOD

PWR_GOOD

PLD_VU_CS/ROM_SEL

PLD_CONF_DONE

PROGRAM_B

PROGRAM_B

MAIN

Buff

Buff

Buff

Buff

IC1105

IC1102, IC1103

IC506

IC1115

IC104

IC102

IC1114

IC1201, IC1202, IC1301, IC1302

IC505

IC504

SPIFlash

Config

ROM

EPR2

JTAG_CN

FILTER

PLL

CDCM

7005

LVDS

BUFF

CN2001

4

4

2x3

4

4

2

NCONF

PLD_RECONFIG

CS/ROM_

SEL

PLD_VU_

PLD_CONF_DONE

Buff

Buff

IC2012

IC2002, IC2003

IC506

FL401

IC408

IC2011

IC2101, IC2102, IC2201, IC2202

IC0701, IC0702, IC0801, IC0802

SPIFlash

Config

ROM

IO

EXP

IO EXP

EEPROM

D/C

SEL

Up/Conv

SEL

4K-RET

12G_CD UHD-SDI A

IC306

J2

12G_CD

UHD-SDI B

IC305 J2

12G CD/EQ

UHD-SDI C

RET_IN

IC307

J2

12G CD/EQ

UHD-SDI D

UHD Prompter_IN

RET_IN

IC308

J2

DEC

TEMP

nCONFIG

PLD_CONF_DONE

NET_CONFOG_SEL

2

4 7

6

NCONF

PW_ON_CONF

PLD_RECONFIG

NET_CONFOG_SEL

VIF_RESERVE(6)

PLD_

VU_

CS

IC1203

IC1204

D1201

SPIFlash

Config

ROM

X501

X0502

VC1002

27MHz

X0501

156.25MHz

VC1001

27MHz

IC1001

100MHz

VC401, VC402

148.5MHz

100MHz

IC502

IC0707, IC0108

Buff

(I/O)

LED

nCONFIG

VUP_SPI(4)

PLD_CONF_DONE

CPU_CLK

REST_FPGA

XRST

CPU_BUS(19)

CPU_CS

4

4

40

BiBi_REF(F/V/H)BiBi_REF(F/V/H)

3

NeNe_REF(F/V/H)

AURORA_RX(10)

PLL_CLK_24

PLL_CLK_27

PLL_CLK_148.5

PLL_CLK_148.35

TG_SYNC(F/V/H)

NTG_DAC

NTG_CLK_27

NeNe_REF(F/V/H)

3

AURORA_TX(10)AURORA_TX(10)

10

AURORA_RX(10)

CLK_156

CLK_390

10

3

NCONF

PW_ON_CONF

PLD_RECONFIG

PLD_

VU_

CS

IC2106

IC2103, IC2104

S0401, IC405

IC2114

D2101

SPIFlash

Config

ROM

Reset IC

IC2105

IC2101

Buff

(I/O)

Buff

(I/O)

LED

DAC

PTP_DAC

PTP_CLK_27

IC1002

IC1004

DAC

EEPROM

IC0501

IC0001

IC1003

IC1006

x2.5

SYNC

LOCK

CLCK

GEN.

100MHz

X1700

IC2201-IC2204

IC1805-IC1808

IC6000

DDR3

1Gb

Buff

Buff

IC1401, IC2308

IC1403

D2300

CN2300

IC300

I2C

IC2315

IC2309

IC2312

IC2306

IC2302, IC2303

256FS

LRCK(FS_48kHz)

AU_DATA(2)

NET_REF(F/V/H)

PWR_GOOD_DPR

PWR_EN_DPR

NET_CONFIG_SEL

PCI Express

XRST(Common), XRST_NET

2

4

O (From/To 3/4)

TX-167A BOARD:

Refer to (4/5)

PWR_GOOD

(For HDCU3500)

MAIN_6GX4

MONI_6GX4

MAIN_3GX2

MONI_3GX2

I2C_SDA/SCL

(From/To 1/5)

(From/To 5/5)

AA

S

(From/To 4/5)

H

(From/To 1/5)

D

(From/To 1/5)

N

(From/To 1/5)

(From/To 2/5)

J

C

(From/To 1/5)

L

(From/To 1/5)

E

(From/To 4/5)

P

(From/To 1/5)

G

(From/To 4/5)

U

(From/To 4/5)

T

(From/To 3/5)

O

HKCU-REC55

IC001

IC001

SGMII

SGMII

8

PCIe

PCIe(GEN2)

6

SGMII

SGMII

8

PCIe

PCIe(GEN2)

6

DDR4

DRAM_I/F(118)

IC1701, IC1702,

IC1801, IC1802

2

2

SFP

2

2

SFP

VC2001

27MHz

IC2001,

IC2002

DAC

CN1001

CN2002

For HDCU5500/

HKCU-FB50

Loading...

Loading...