102 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

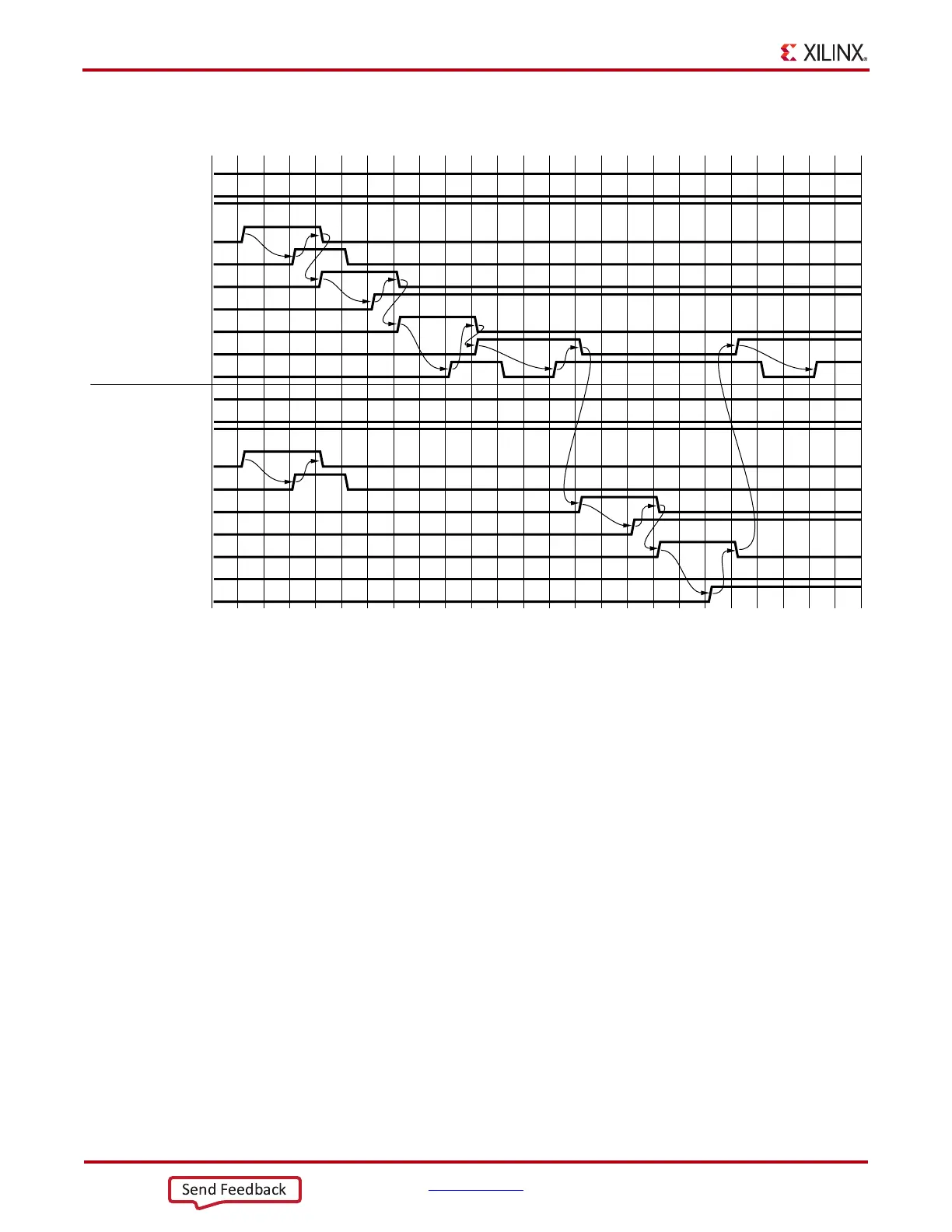

Figure 3-15 shows the required steps to perform TX phase and delay alignment.

Notes relevant to Figure 3-15:

1. The sequence of events shown in Figure 3-15 is not drawn to scale.

2. M_* denotes ports related to the master lane.

3. S_* denotes ports related to the slave lane(s).

4. GTP transceiver: Set the TXSYNC_OVRD attribute to 1'b1.

5. Set TXPHDLYRESET and TXDLYBYPASS to Low for all lanes.

6. Set TXPHALIGNEN to High for all lanes.

7. Assert TXDLYSRESET for all lanes. Hold this signal High until TXDLYSRESETDONE of the

respective lane is asserted.

8. Deassert TXDLYSRESET for the lane in which the TXDLYSRESETDONE is asserted.

9. When TXDLYSRESET of all lanes are deasserted, assert TXPHINIT for the master lane. Hold

this signal High until the rising edge of TXPHINITDONE of the master lane is observed.

10. Deassert TXPHINIT for the master lane.

11. Assert TXPHALIGN for the master lane. Hold this signal High until the rising edge of

TXPHALIGNDONE of the master lane is observed.

12. Deassert TXPHALIGN for the master lane.

13. Assert TXDLYEN for the master lane. This causes TXPHALIGNDONE to be deasserted.

14. Hold TXDLYEN for the master lane High until the rising edge of TXPHALIGNDONE of the

master lane is observed.

X-Ref Target - Figure 3-15

Figure 3-15: TX Phase and Delay Alignment, Multi-Lane Mode

M_TXPHDLYRESET

M_TXDLYBYPASS

M_TXPHALIGNEN

M_TXDLYSRESET

M_TXDLYSRESETDONE

M_TXPHINIT

M_TXPHINITDONE

M_TXPHALIGN

M_TXDLYEN

M_TXPHALIGNDONE

S_TXPHDLYRESET

S_TXDLYBYPASS

S_TXPHALIGNEN

S_TXDLYSRESET

S_TXDLYSRESETDONE

S_TXPHINIT

S_TXPHINITDONE

S_TXPHALIGN

S_TXDLYEN

S_TXPHALIGNDONE

UG482_c3_116_020413

Loading...

Loading...