166 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

Ports and Attributes

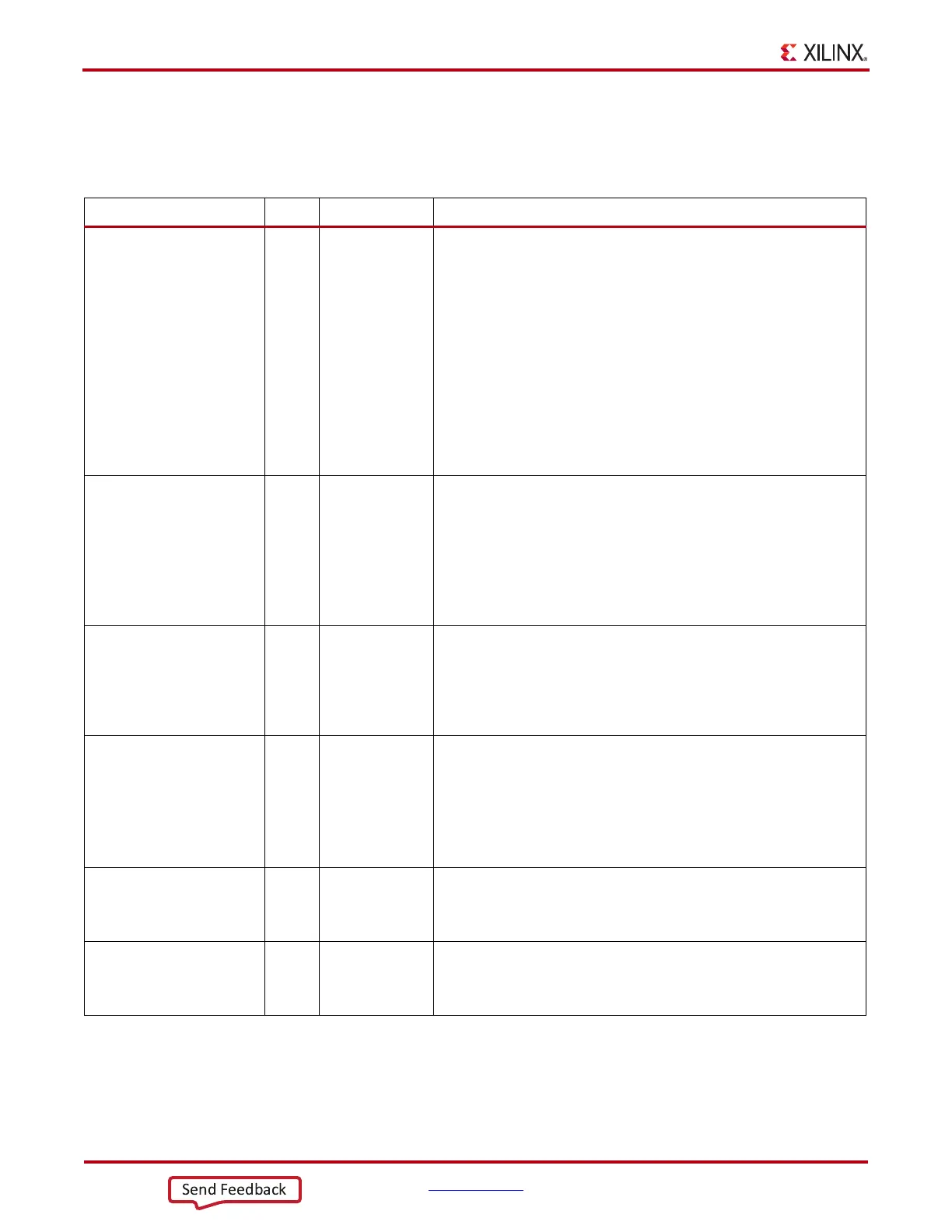

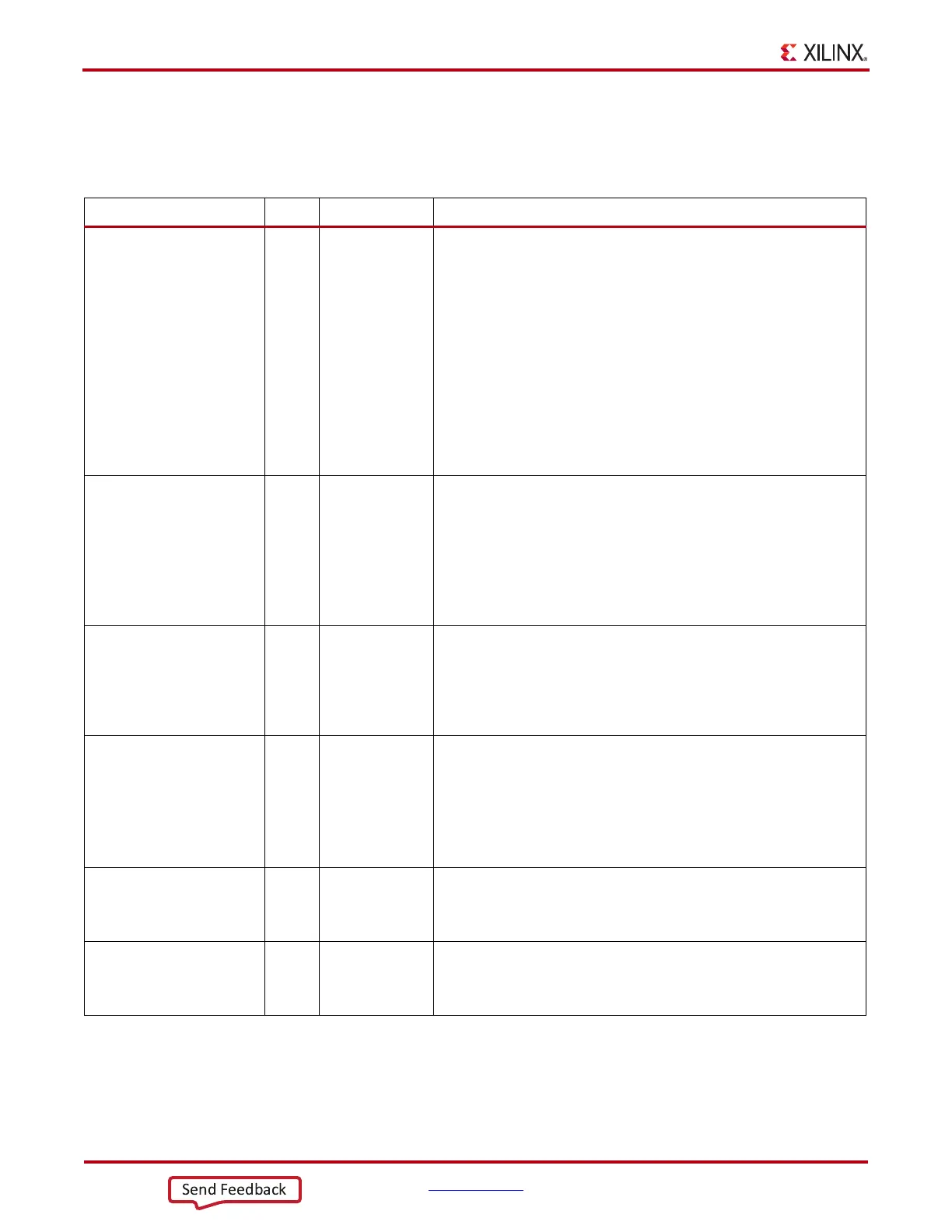

Table 4-25 defines the RX byte and word alignment ports.

Table 4-25: RX Byte and Word Alignment Ports

Port Name Dir Clock Domain Description

RXBYTEISALIGNED Out RXUSRCLK2 This signal from the comma detection and realignment circuit is High

to indicate that the parallel data stream is properly aligned on byte

boundaries according to comma detection.

0: Parallel data stream not aligned to byte boundaries

1: Parallel data stream aligned to byte boundaries

There are several cycles after RXBYTEISALIGNED is asserted before

aligned data is available at the FPGA RX interface.

RXBYTEISALIGNED responds to plus comma alignment when

RXPCOMMAALIGNEN is TRUE. RXBYTEISALIGNED responds

to minus comma alignment when RXMCOMMAALIGNEN is TRUE.

Some conditions when this signal could deviate from the expected

behavior are discussed in Alignment Status Signals, page 163.

RXBYTEREALIGN Out RXUSRCLK2 This signal from the comma detection and realignment circuit indicates

that the byte alignment within the serial data stream has changed due to

comma detection.

0: Byte alignment has not changed

1: Byte alignment has changed

Data can be lost or repeated when alignment occurs, which can cause

data errors (and disparity errors when the 8B/10B decoder is used).

RXCOMMADET Out RXUSRCLK2 This signal is asserted when the comma alignment block detects a

comma. The assertion occurs several cycles before the comma is

available at the FPGA RX interface.

0: Comma not detected

1: Comma detected

RXCOMMADETEN In RXUSRCLK2 RXCOMMADETEN activates the comma detection and alignment

circuit.

0: Bypass the circuit

1: Use the comma detection and alignment circuit

Bypassing the comma and alignment circuit reduces RX datapath

latency.

RXPCOMMAALIGNEN In RXUSRCLK2 Aligns the byte boundary when comma plus is detected.

0: Disabled

1: Enabled.

RXMCOMMAALIGNEN In RXUSRCLK2 Aligns the byte boundary when comma minus is detected.

0: Disabled

1: Enabled.

Loading...

Loading...