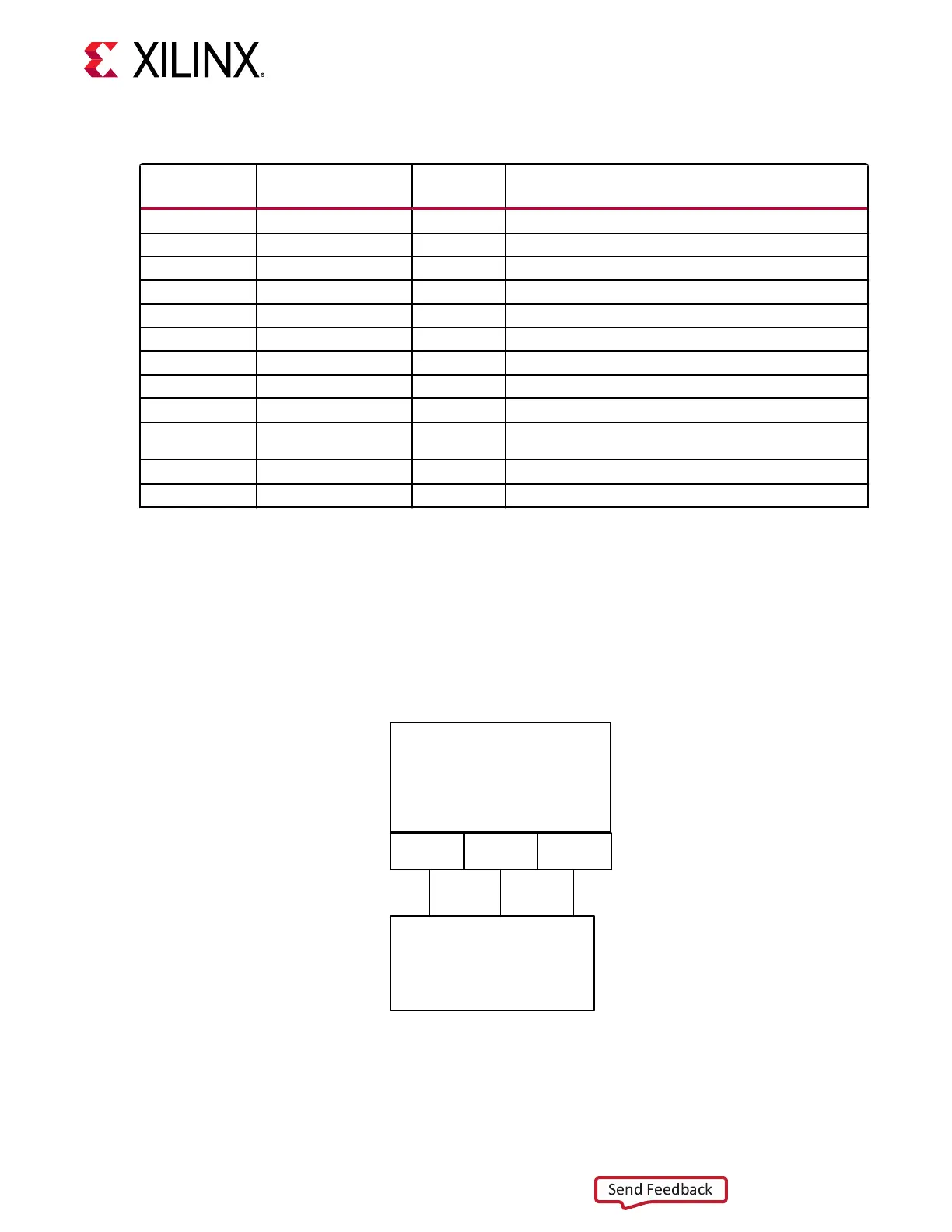

Table 6: I/O Voltage Rails (cont'd)

ACAP (U1)

Bank

Power Supply Rail

Net Name

Voltage Description

XPIO Bank 703 VCC1V1_LP4 1.1V LPDDR4_3_DQ[0:7, 16:23], ADDR/CTRL

XPIO Bank 704 VCC1V1_LP4 1.1V LPDDR4_2_DQ[0:7, 16:23]; LPDDR4_3_DQ[8:15, 24:31]

XPIO Bank 705 VCC1V1_LP4 1.1V LPDDR4_2_DQ[8:15, 24:31], ADDR/CTRL; Si570 U3 200 MHz

XPIO Bank 706 VADJ_FMC 1.5V 8A34001_GPIO_[0:15]; FMCP1_LA[00:16]

XPIO Bank 707 VADJ_FMC 1.5V FMCP1_LA[17:33]; FMCP2_LA[26:33]

XPIO Bank 708 VADJ_FMC 1.5V FMCP2_LA[00:25]

XPIO Bank 709 VCC1V1_LP4 1.1V LPDDR4_1_DQ[0:7, 16:23], ADDR/CTRL

XPIO Bank 710 VCC1V1_LP4 1.1V LPDDR4_0_DQ[0:7, 16:23]; LPDDR4_1_DQ[8:15, 24:31]

XPIO Bank 711 VCC1V1_LP4 1.1V LPDDR4_0_DQ[8:15, 24:31], ADDR/CTRL; Si570 U4 200 MHz

PMC MIO 500 VCCO_500 3.3V SYSMON IF; PMC_MIO[0:25]_500; ISL60002 U6 1.042V VREF;

J1 2x6 SYSMON PIN HDR

PMC MIO 501 VCCO_501 3.3V PMC_MIO[26:51]

LP MIO 502 VCCO_502 3.3V LPD_MIO[0:25]

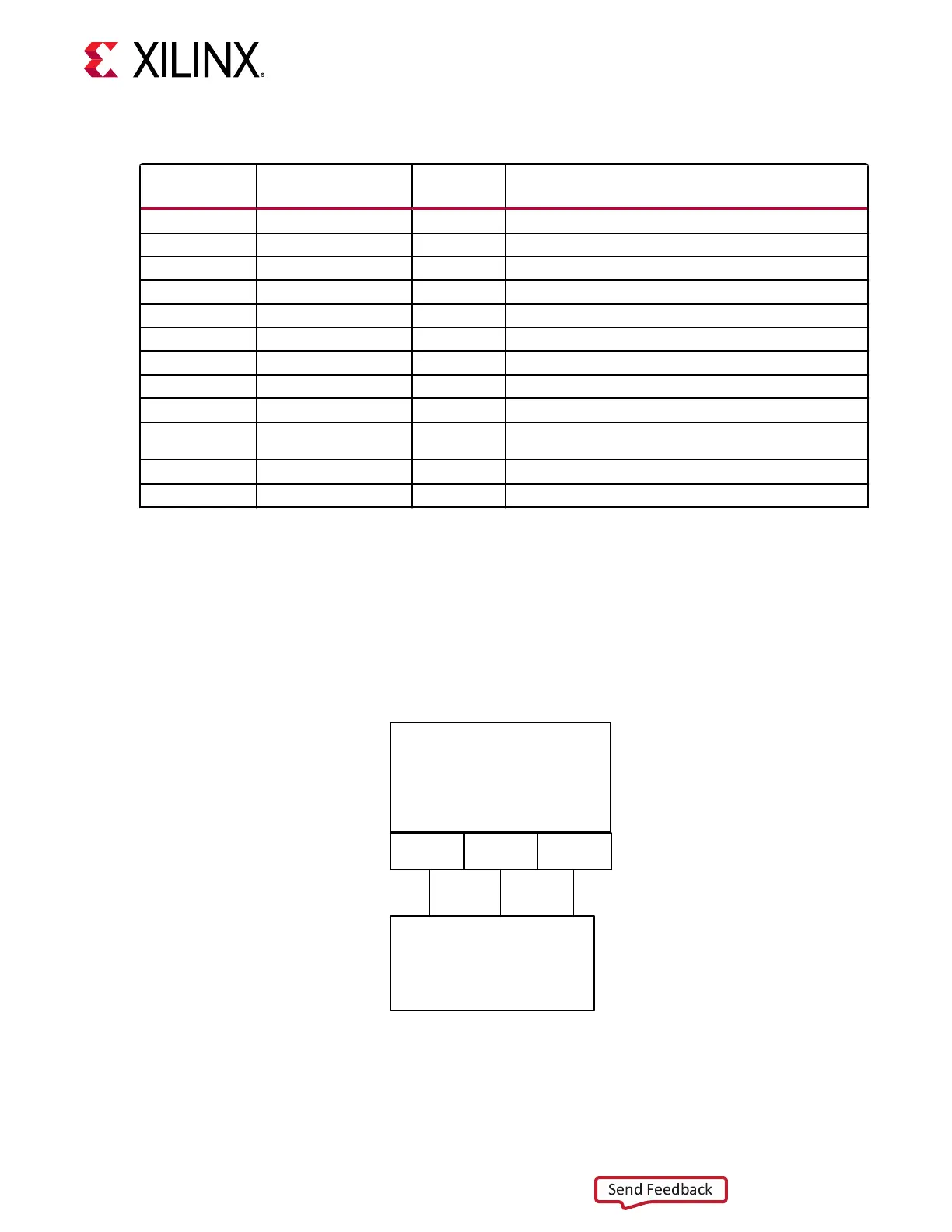

DDR4 UDIMM Socket

[Figure 3, callout 1]

The VCK190 board XPIO triplet 1 (banks 700/701/702) memory interface supports 288-pin 72-

bit DDR4 DIMM socket J45.

Figure 6: DDR4 DIMM Memory

XPIO

Triplet 1

700 701 702

DDR4 72-bit

UDIMM

X23197-120120

The VCK190 board is shipped with a DDR4 UDIMM installed:

• Manufacturer: Micron

Chapter 3: Board Component Descriptions

UG1366 (v1.0) January 7, 2021 www.xilinx.com

VCK190 Board User Guide 25

Loading...

Loading...