Do you have a question about the Xilinx VCK190 Series and is the answer not in the manual?

| Manufacturer | Xilinx |

|---|---|

| Series | VCK190 |

| FPGA Family | Versal |

| Memory | DDR4 |

| PCIe | Gen4 x16 |

| Chipset | Versal |

| Storage | SATA |

| USB Ports | USB 3.0 |

Introduces the VCK190 evaluation board and its capabilities.

Explains how the document is organized by design processes.

Lists external documents and resources for further information.

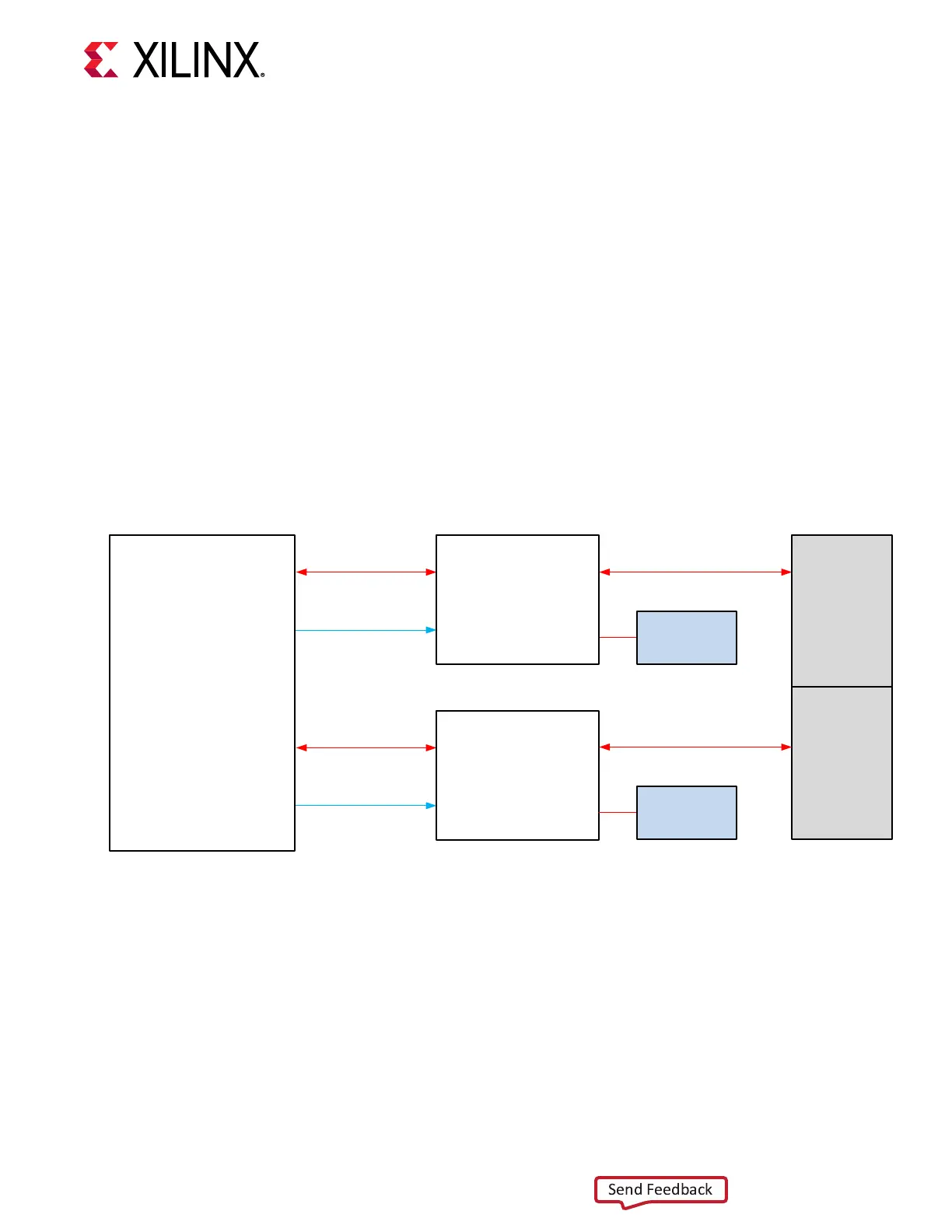

Provides a high-level visual representation of board components.

Details the key hardware features and capabilities of the VCK190 board.

Outlines the physical dimensions and environmental operating parameters.

Provides essential precautions for handling electronic components safely.

Identifies the physical locations of components on the VCK190 board.

Specifies the default configurations for jumpers and switches.

Details the boot modes and configuration options for the Versal ACAP.

Provides a detailed functional description of board components and features.

Describes the Versal ACAP, DDR4 UDIMM, and LPDDR4 memory systems.

Details MIO, USB, SD, CAN, UART, I2C, and Ethernet interfaces.

Covers clock sources, GTY transceivers, PCIe, FMC, SFP, QSFP, and HDMI.

Explains power rails, LEDs, fan control, system controller, and switches.

Introduces the FMC+ connector pinout defined by VITA 57.4.

Details the pinout of the FPGA Mezzanine Card (FMC) HSPC connector.

Explains the purpose and usage of XDC files for the VCK190 board.

Provides guidance on using XDC files for VCK190 board designs.

Introduces the Pmod FMC board for accessing Pmod devices.

Details the mapping between Pmod and FMC connector pins.

Lists relevant EU directives and standards for CE compliance.

Explains WEEE, RoHS, and CE compliance markings.

Provides links to support resources like Answers, Docs, and Forums.

Explains how to access Xilinx documents and design resources.

Lists supplemental documents and external resources for the VCK190.

Contains disclaimers, warranty information, and usage terms.