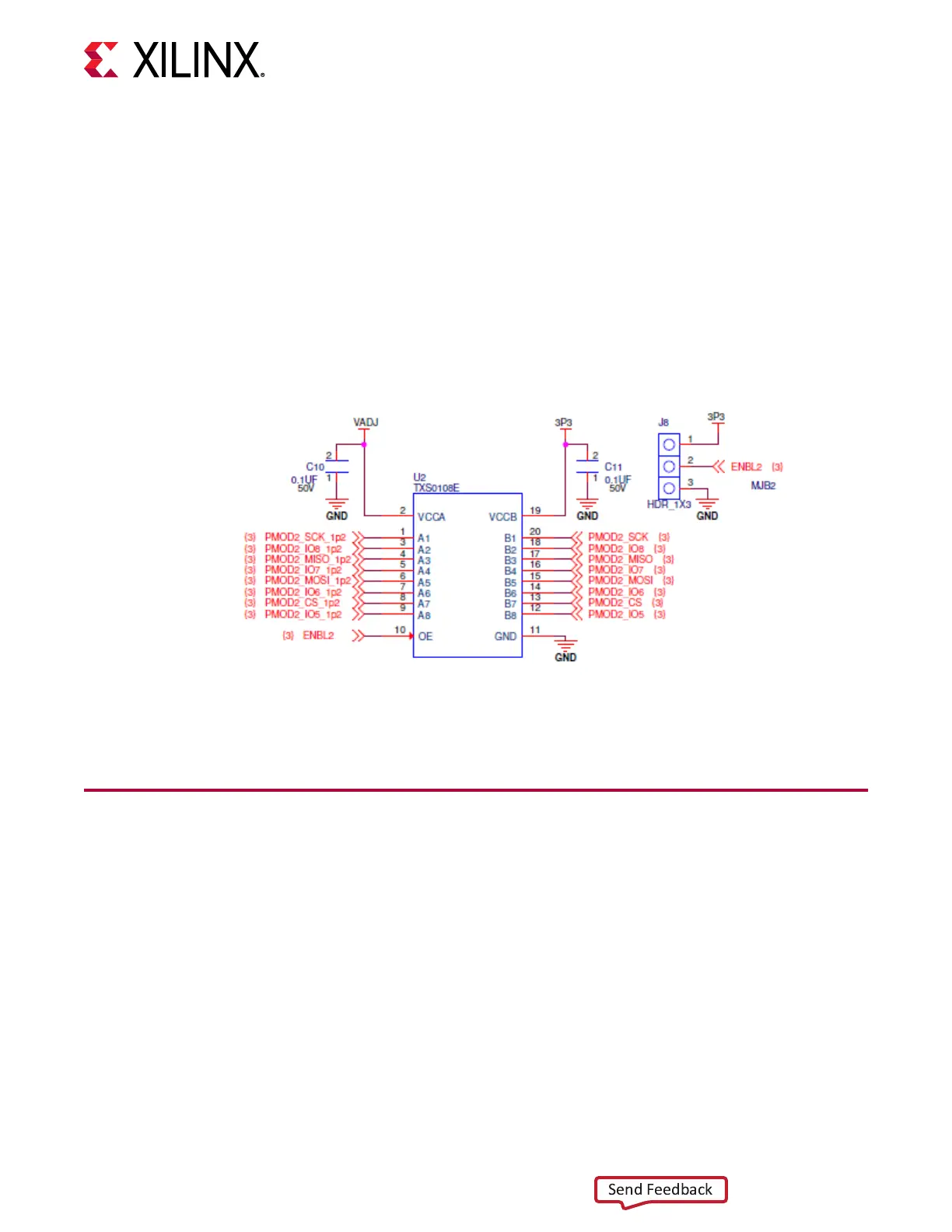

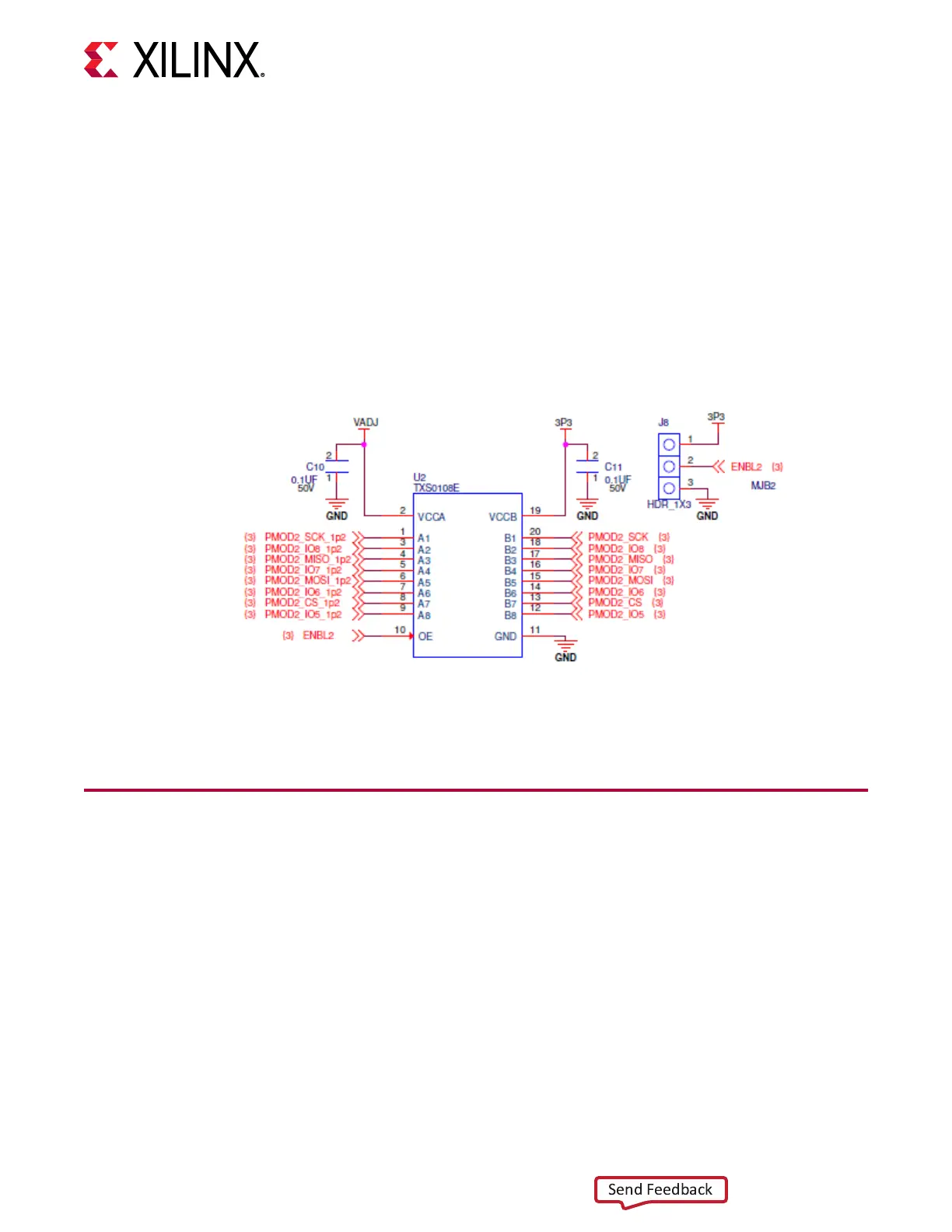

The voltage translators shown in the gure are the TXS0108E 8-bit bidireconal level shier

voltage translators for open drain and push-pull applicaons. The input voltage for the I/O to the

level translator is controlled from the VADJ, which operates in the range of 1.5V to 3.3V. With

the Versal ACAP, the I/O voltage on the XPIO (which is the primary I/O of the FMC) is a

maximum of 1.5V, so the default seng for using this FMC Pmod card is VADJ = 1.5V on the

XPIO I/O. On the output side of the level translator, this is converted to a 3.3V signal because

the Pmod specicaon is at 3.3V. 5V is also supported per the Pmod specicaon, but this

voltage is not supported without modicaon to the output power supplies of the level

translator, which are xed at 3.3V for the XM119 FMC board.

Figure 29: TXS0108E Bidirectional Voltage Level Translator

X24766-102620

Note: This level translator was specically chosen to allow bidireconal signaling at lower frequencies, such

as for I2C. The Pmod board is generic and can work with both the VCK190 and VMK180 development

kits. The pinouts are idencal between the boards, and usage should be straighorward.

Pin Mapping Pmod to FMC

The pin mapping is straighorward. The ACAP pins are connected to the input to the level

translators, which map to the output pins on the Pmod connector at 3.3V. See Figure 29 for

details.

Appendix C: Pmod FMC

UG1366 (v1.0) January 7, 2021 www.xilinx.com

VCK190 Board User Guide 72

Loading...

Loading...