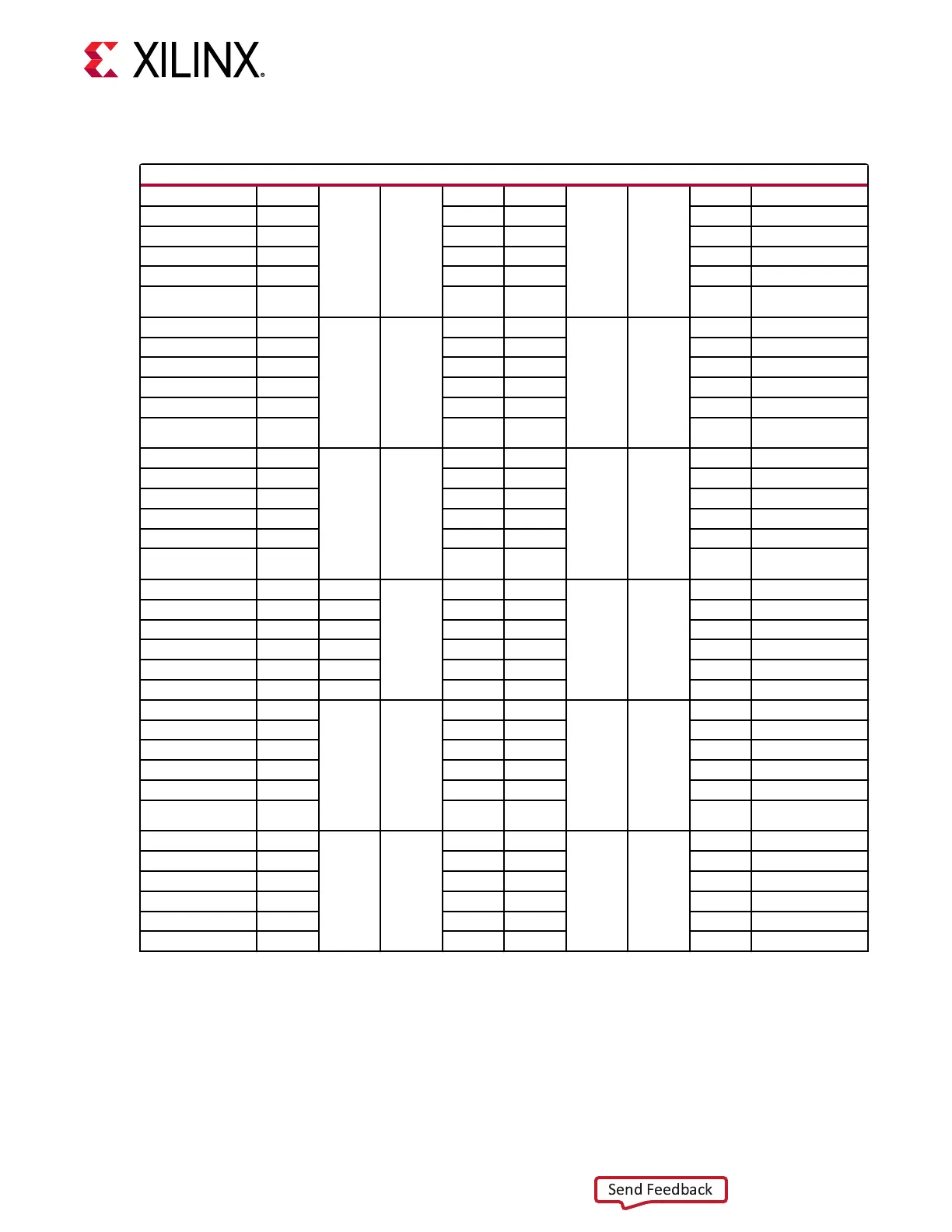

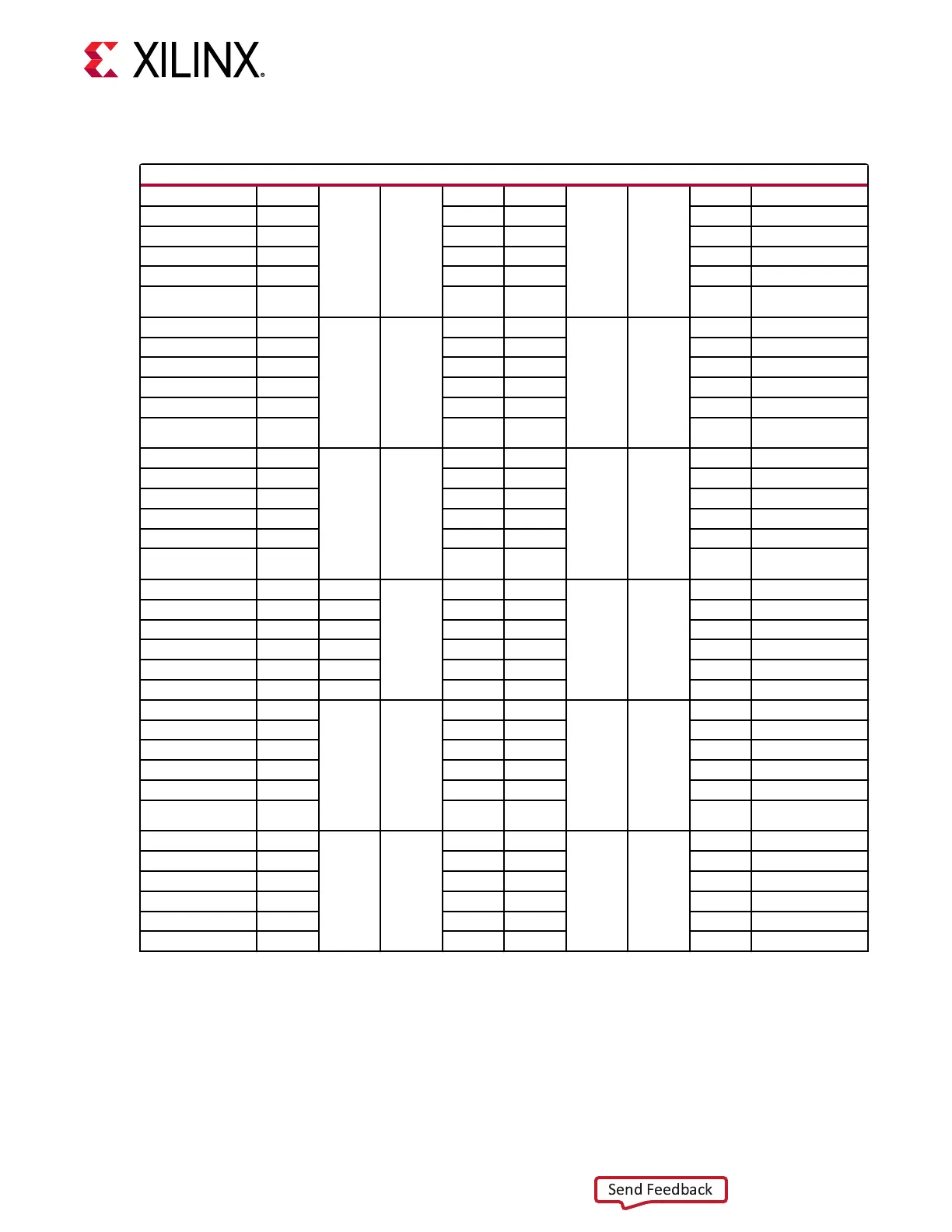

Table 18: GTY Mapping (cont'd)

VCK190 XC10S80 VSVA2197 GTY Mapping

SFP1 ch3

GTYT_M

Quad 105

PCIe PCIe

GTYT_S

Quad 205

ch3 FMC2 DP7

SFP0 ch2 ch2 FMC2 DP6

None ch1 ch1 FMC2 DP5

HSDP (USB-C) ch0 ch0 FMC2 DP4

HSDP SI570 CLK refclk1 refclk1 FMC2_GBTCLK1

zSFP SI570 CLK refclk0 refclk0

SI570_8A34001_MUX_BU

F2

PCIe Lane 7 ch3

GTYB_M

Quad 104

PCIe MRMAC

GTYB_S

Quad 204

ch3 FMC2 DP3

PCIe Lane 6 ch2 ch2 FMC2 DP2

PCIe Lane 5 ch1 ch1 FMC2 DP1

PCIe Lane 4 ch0 ch0 FMC2 DP0

None refclk1 refclk1 FMC2_GBTCLK0

PCIe Slot Clock 0

(buffered)

refclk0 refclk0

SI570_8A34001_MUX_BU

F1

PCIe Lane 3 ch3

GTYT_S

Quad 103

CPMG4 MRMAC

GTYT_M

Quad 203

ch3 FMC1 DP11

PCIe Lane 2 ch2 ch2 FMC1 DP10

PCIe Lane 1 ch1 ch1 FMC1 DP9

PCIe Lane 0 ch0 ch0 FMC1 DP8

NONE refclk1 refclk1 FMC1_GBTCLK2

PCIe Slot Clock 0

(buffered)

refclk0 refclk0 None

CPMG4 PCIe

GTYB_M

Quad 202

ch3 FMC1 DP7

ch2 FMC1 DP6

ch1 FMC1 DP5

ch0 FMC1 DP4

refclk1 FMC1_GBTCLK1

refclk0 None

MRMAC

GTYT_S

Quad 201

ch3 FMC1 DP3

ch2 FMC1 DP2

ch1 FMC1 DP1

ch0 FMC1 DP0

refclk1 FMC1_GBTCLK0

refclk0

SI570_8A34001_MUX_BU

F0

MRMAC

GTYB_S

Quad 200

ch3 QSFP4

ch2 QSFP3

ch1 QSFP2

ch0 QSFP1

refclk1 IEEE-1588 Clock

refclk0 IEEE-1588 Clock

The GTY connecons are shown in the following gure.

Chapter 3: Board Component Descriptions

UG1366 (v1.0) January 7, 2021 www.xilinx.com

VCK190 Board User Guide 51

Loading...

Loading...