110 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

Ports and Attributes

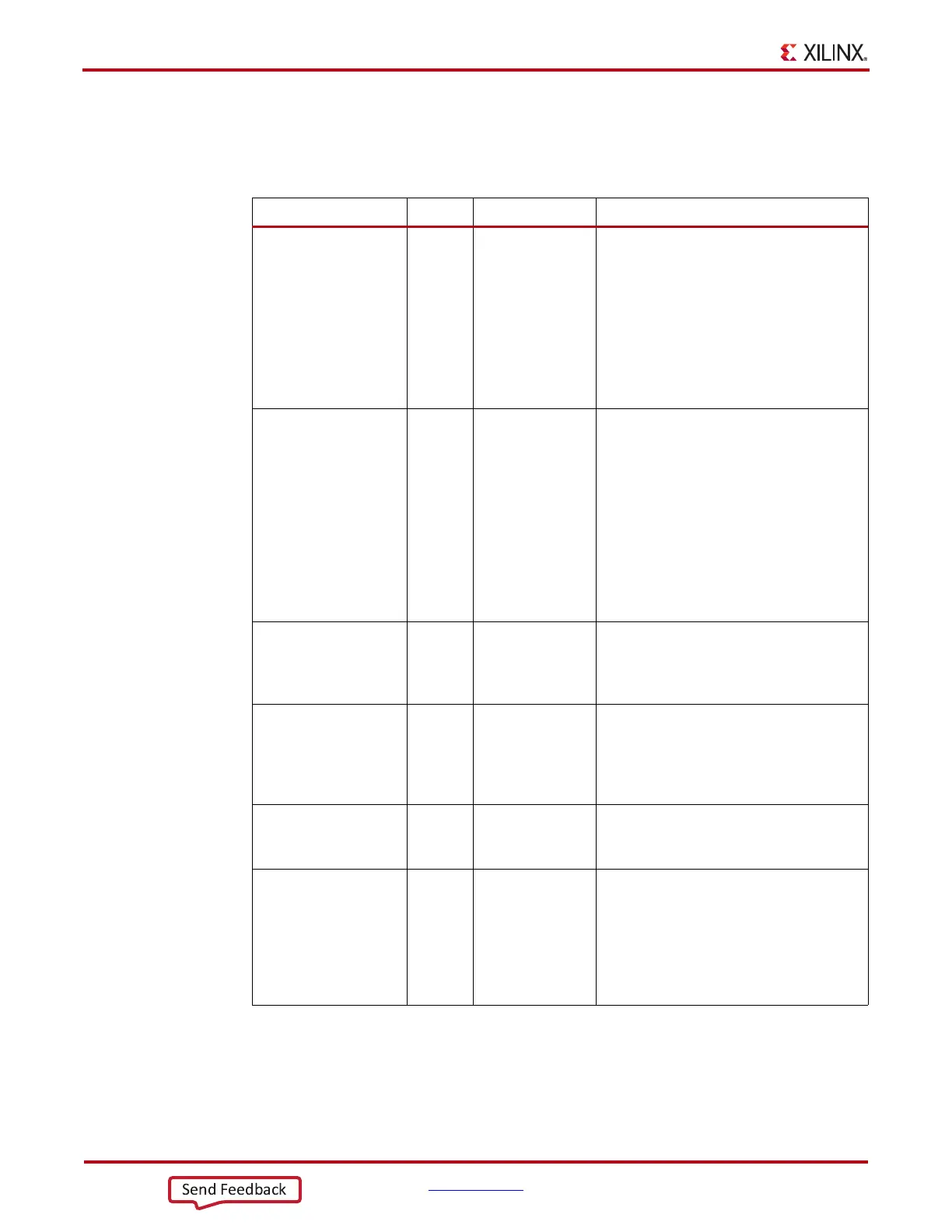

Table 3-24 defines the ports required for TX fabric clock output control.

Table 3-24: TX Fabric Clock Output Control Ports

Port Dir Clock Domain Description

TXOUTCLKSEL[2:0] In Async This port controls the multiplexer select

signal in

Figure 3-20.

3'b000: Static 1

3'b001: TXOUTCLKPCS path

3'b010: TXOUTCLKPMA path

3'b011: TXPLLREFCLK_DIV1 path

3'b100: TXPLLREFCLK_DIV2 path

Others: Reserved.

TXRATE[2:0] In TXUSRCLK2

(TXRATEMODE

makes this port

asynchronous)

This port dynamically controls the setting

for the TX serial clock divider D (see

Table 3-23), and it is used with the

TXOUT_DIV attribute.

3'b000: Use the TXOUT_DIV divider

value

3'b001: Set the D divider to 1

3'b010: Set the D divider to 2

3'b011: Set the D divider to 4

3'b100: Set the D divider to 8

TXOUTCLKFABRIC Out Clock TXOUTCLKFABRIC is a redundant output

reserved for testing. TXOUTCLK with

TXOUTCLKSEL = 3'b011 should be

used instead.

TXOUTCLK Out Clock TXOUTCLK is the recommended clock

output to the FPGA logic. The

TXOUTCLKSEL port is the input selector

for TXOUTCLK and allows the PLL input

reference clock to the FPGA logic.

TXOUTCLKPCS Out Clock TXOUTCLKPCS is a redundant output.

TXOUTCLK with TXOUTCLKSEL =

3'b001 should be used instead.

TXRATEDONE Out TXUSRCLK2 The TXRATEDONE port is asserted High

for one TXUSRCLK2 cycle in response to a

change on the TXRATE port. The

TRANS_TIME_RATE attribute defines the

period of time between a change on the

TXRATE port and the assertion of

TXRATEDONE.

Loading...

Loading...