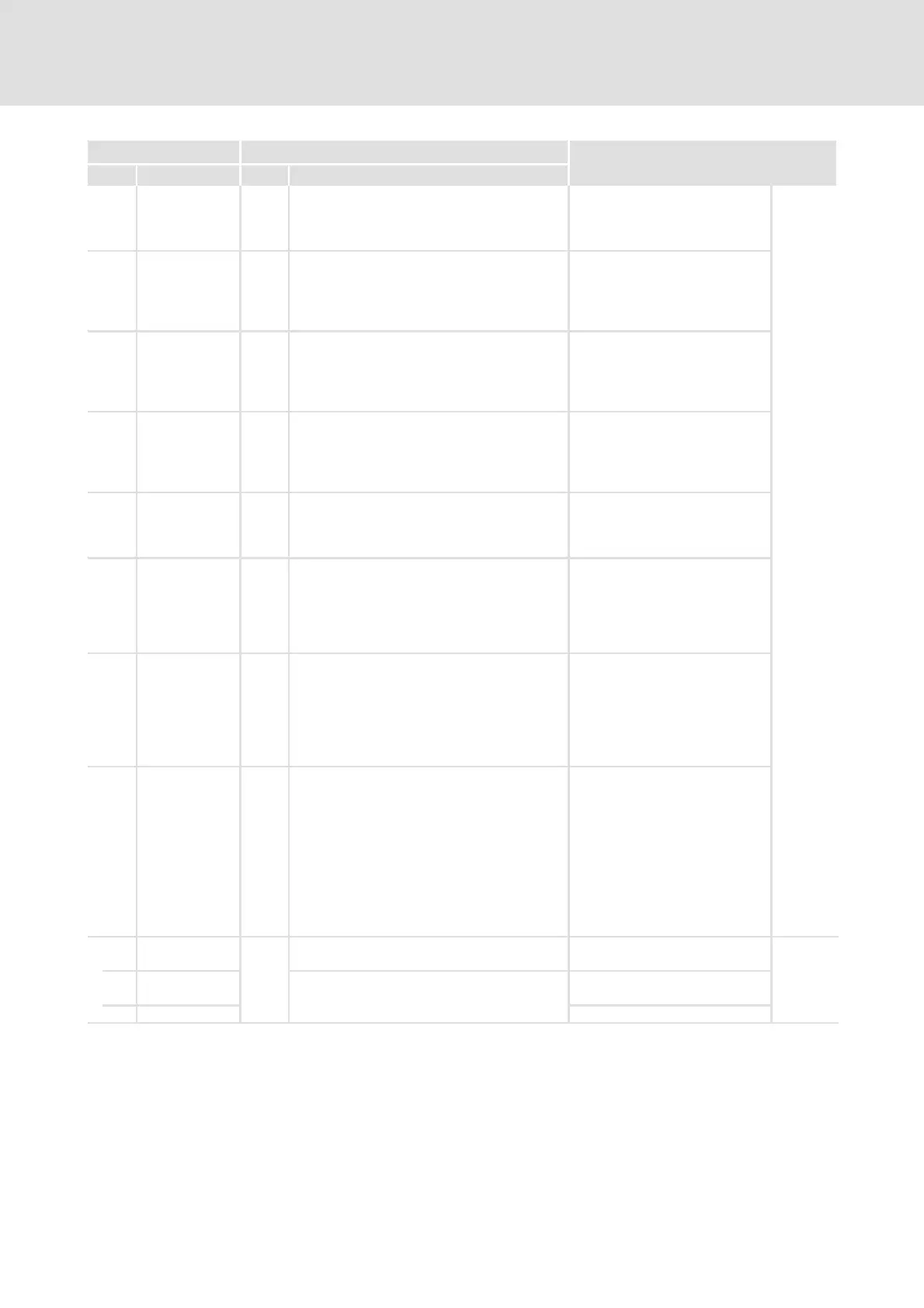

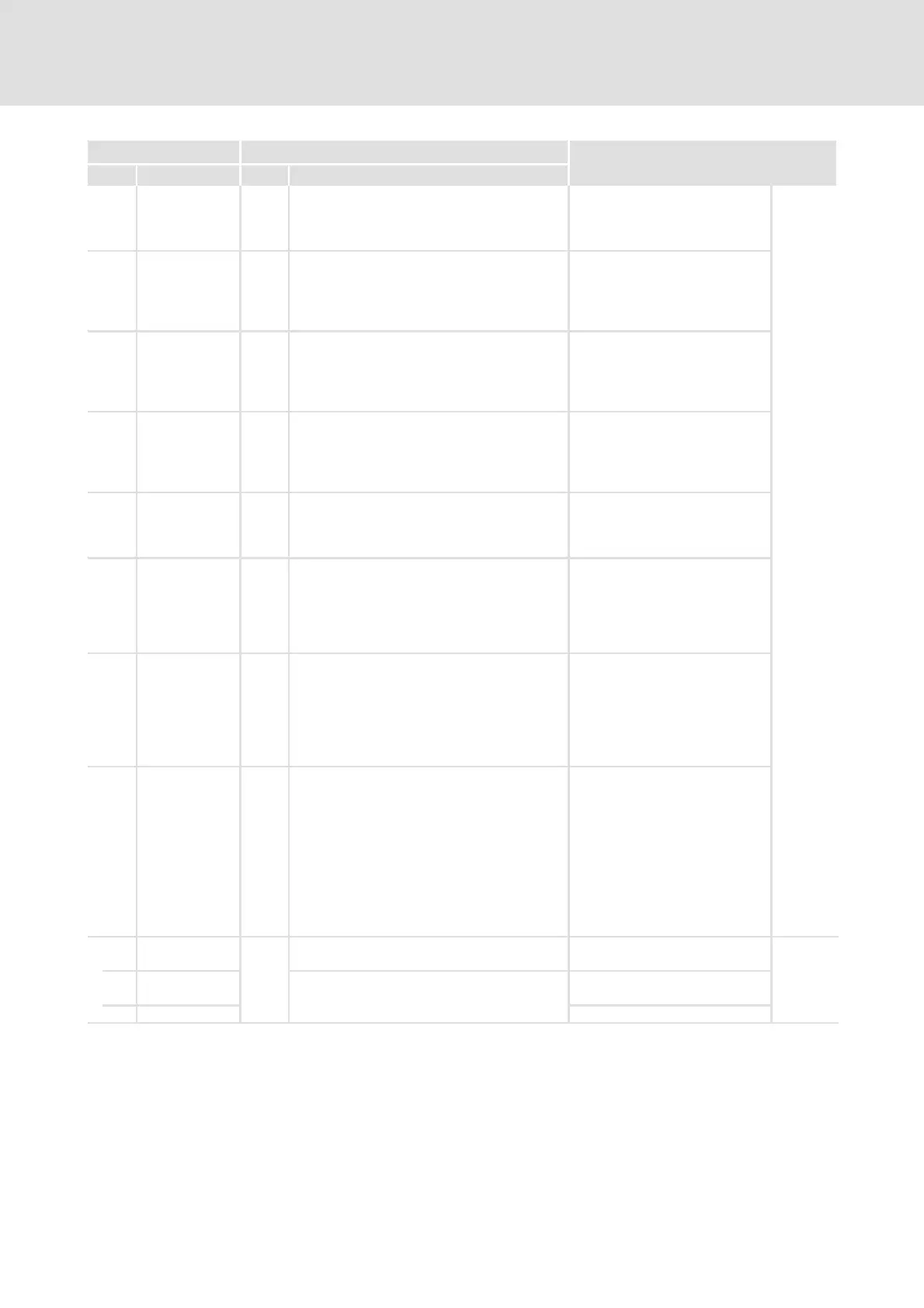

Configuration

Code table

8

8.3

8.3-31

EDSVF9333V EN 3.0-06/2005

IMPORTANTPossible settingsCode

SelectionLenzeNameNo.

C0520

CFG: IN 1000 FIXEDPHI-0 Selection list 4 Configuration of input signal,

function block DFSET

z Input of speed / phase

setpoint signal

8.2-18

C0521

CFG: VP-DIV 1000 FIXED0% Selection list 1 Configuration of analog input

signal, function block DFSET

z Signal for numerator of

stretching factor

z 100 % = 16384 inc

C0522

cfg: rat-div 1000 FIXED0% Selection list 1 Configuration of analog input

signal, function block DFSET

z Signal for numerator of

gearbox factor

z 100 % = 16384 inc

C0523

cfg: A-trim 1000 FIXED0% Selection list 1 Configuration of analog input

signal, function block DFSET

z Signal for phase trimming via

offset multiplier (C0529)

z 100 % = 16384 inc

C0524

cfg: n-trim 1000 FIXED0% Selection list 1 Configuration of analog input

signal, function block DFSET

z Signal for speed trimming

z Signal in [%] of C0011

C0525

cfg: 0-pulse 1000 FIXED0 Selection list 2 Configuration of digital input

signal, function block DFSET

z Signal for one-time zero pulse

activation

z HIGH = release for zero pulse

synchronisation

C0526

CFG: RESET 1000 FIXED0 Selection list 2 Configuration of digital input

signal, function block DFSET

z Signal for reset of integrators

z HIGH sets

– Position difference = 0

–DFSET-PSET=0

– DFSET-PSET2=0

C0527

CFG: SET 1000 FIXED0 Selection list 2 Configuration of digital input

signal, function block DFSET

z HIGH = Set phase integrators

to equal values

z LOW-HIGH edge sets

DFSET-PSET = 0

z HIGH-LOW edge sets

DFSET-PSET to the current

value of MCTRL-PHI-SET

z DFSET-SET has a higher priority

than DFSET-RESET

C0528 -2

.

10

9

{1} 2

.

10

9

Function block DFSET

z Display only

8.2-18

1 DIS: 0-pulse A Phase difference between two

zero pulses

2 DIS: Offset Offset = C0523 × C0529 + C0252

Loading...

Loading...