Clock Generator Module (CGM)

Functional Description

MC68HC908AB32 — Rev. 1.0 Technical Data

MOTOROLA Clock Generator Module (CGM) 133

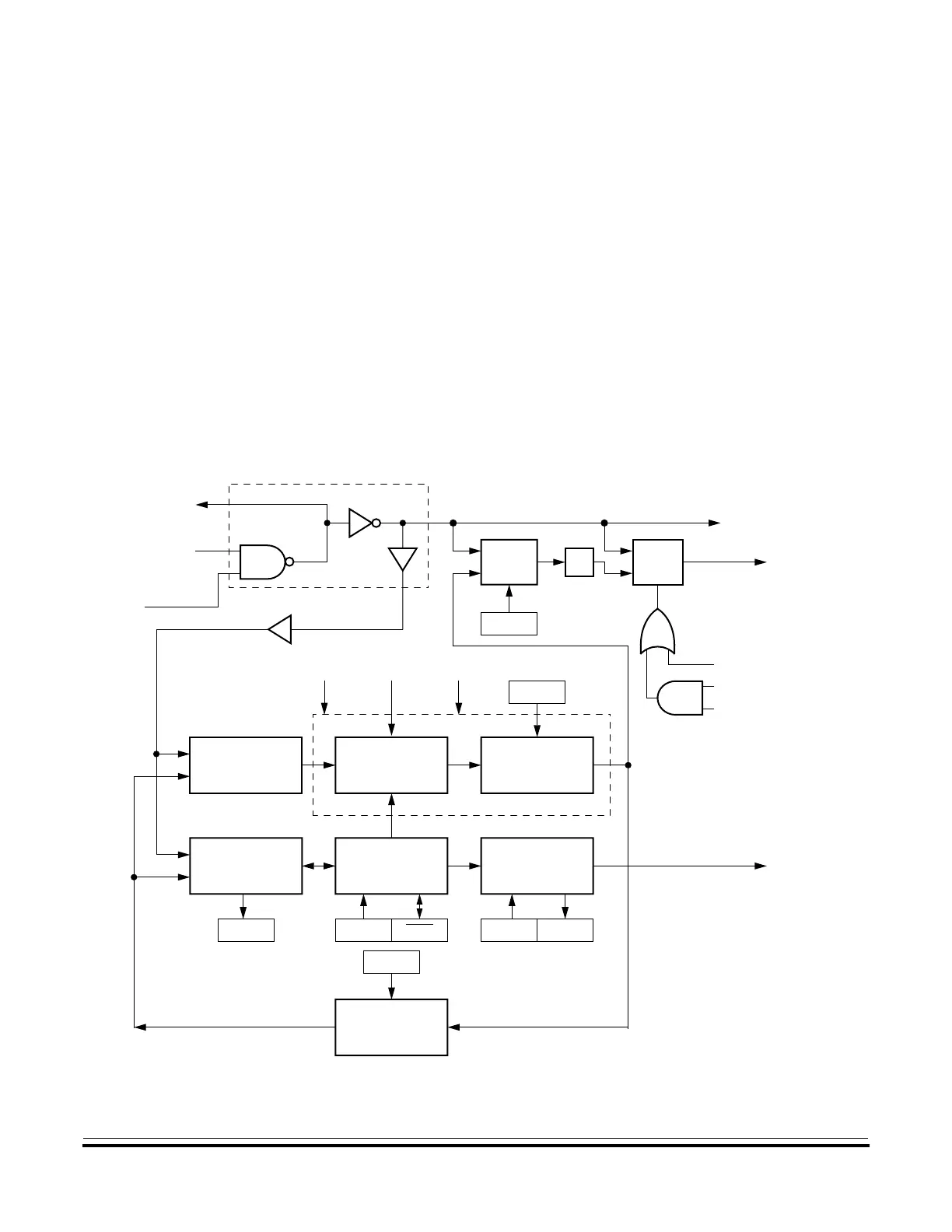

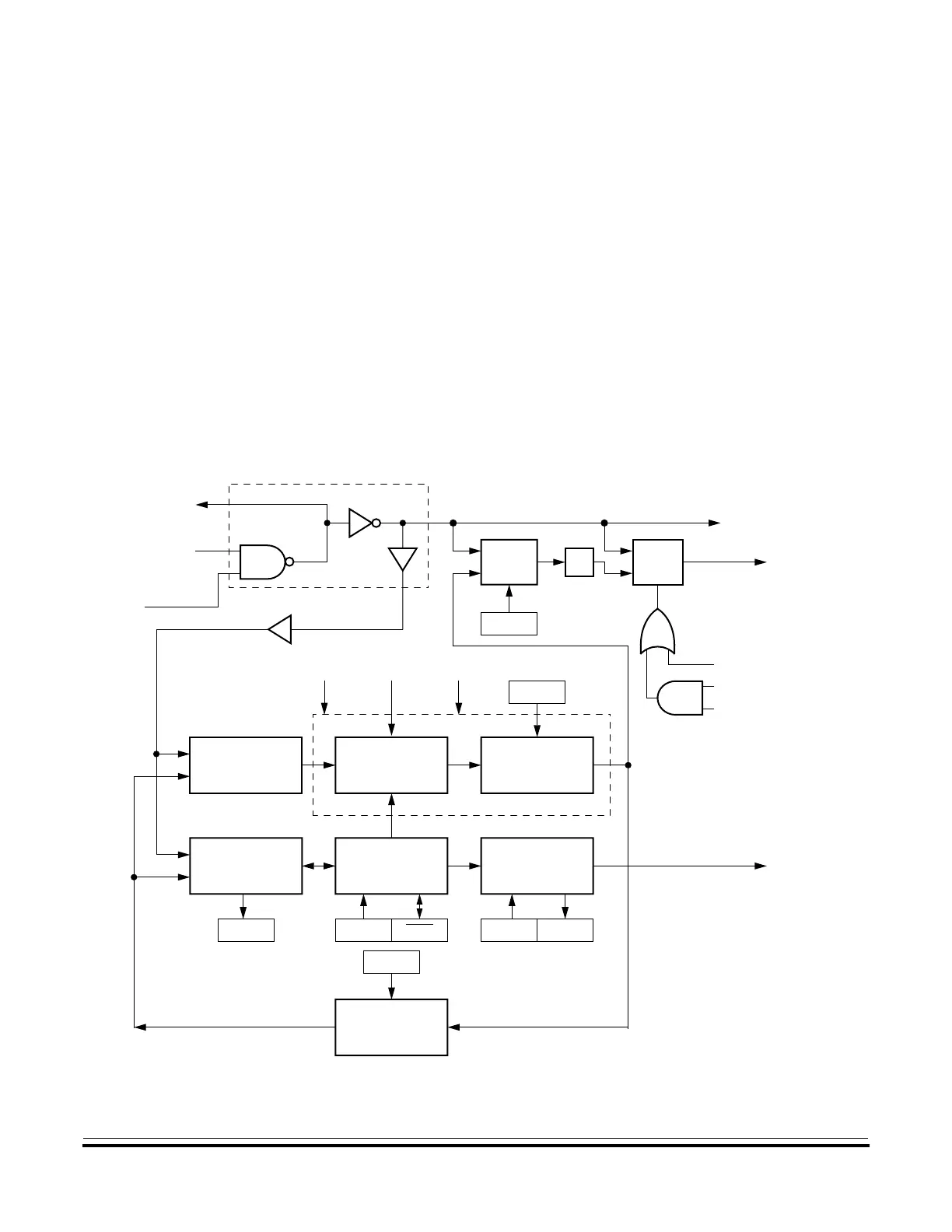

9.4 Functional Description

The CGM consists of three major sub-modules:

• Crystal oscillator circuit which generates the constant crystal

frequency clock, CGMXCLK.

• Phase-locked loop (PLL) which generates the programmable

VCO frequency clock CGMVCLK.

• Base clock selector circuit; this software-controlled circuit selects

either CGMXCLK divided by two or the VCO clock CGMVCLK

divided by two, as the base clock CGMOUT. The SIM derives the

system clocks from CGMOUT.

Figure 9-1 shows the structure of the CGM.

Figure 9-1. CGM Block Diagram

BCS

PHASE

DETECTOR

LOOP

FILTER

FREQUENCY

DIVIDER

VOLTAGE

CONTROLLED

OSCILLATOR

BANDWIDTH

CONTROL

LOCK

DETECTOR

CLOCK

CGMXCLK

CGMOUT

CGMVDV CGMVCLK

SIMOSCEN

CRYSTAL OSCILLATOR

INTERRUPT

CONTROL

CGMINT

CGMRDV

PLL ANALOG

÷2

CGMRCLK

SELECT

CIRCUIT

LOCK AUTO ACQ

VRS[7:4]

PLLIE PLLF

MUL[7:4]

TO SIM, SCI

TO SIM

MONITOR MODE

A

B

S*

USER MODE

*When S = 1, CGMOUT = B

OSC1

OSC2

V

DDA

CGMXFC V

SS

PTC3

Loading...

Loading...