Serial Communications Interface

Technical Data MC68HC908AB32 — Rev. 1.0

256 Serial Communications Interface Module (SCI) MOTOROLA

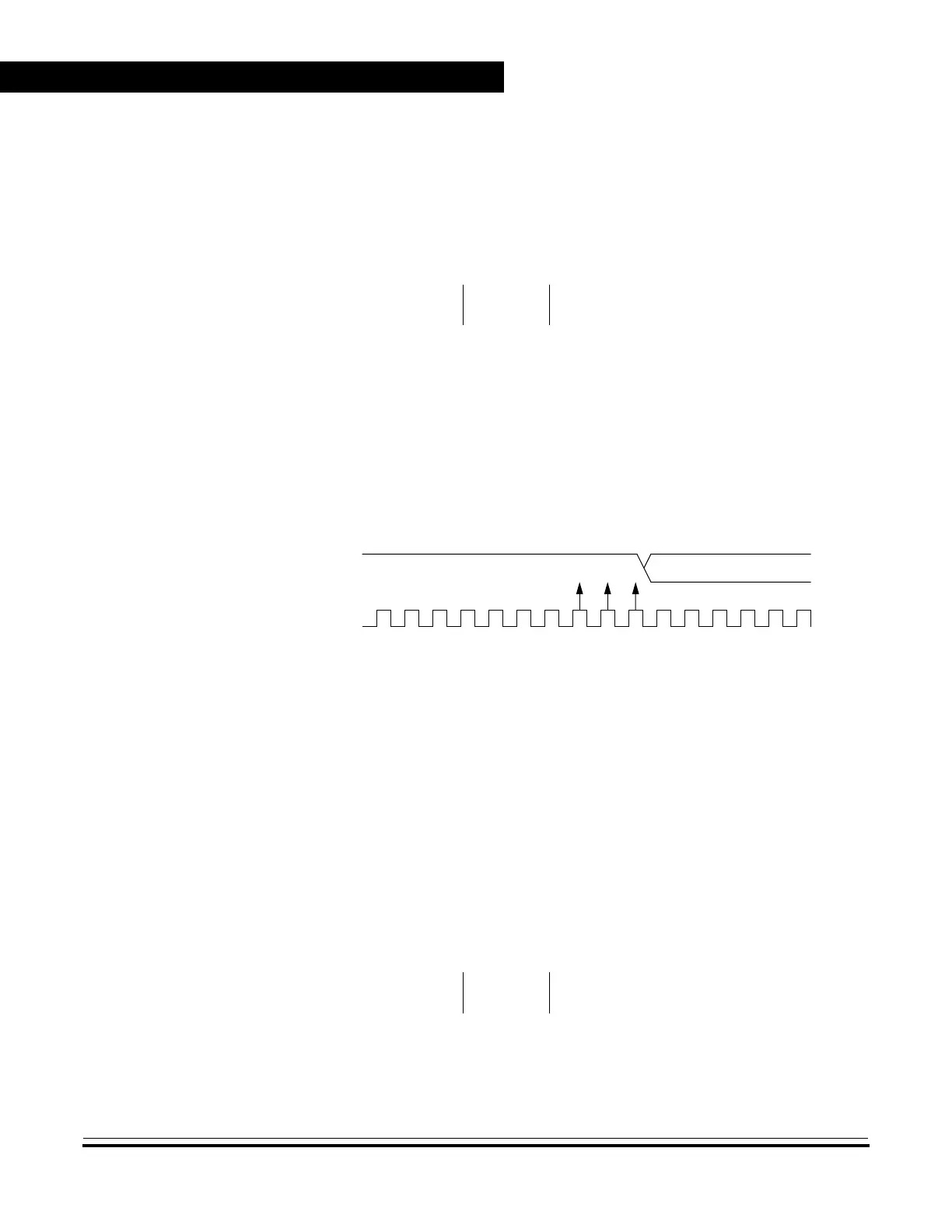

With the misaligned character shown in Figure 15-7, the receiver counts

170 RT cycles at the point when the count of the transmitting device is

10 bit times × 16 RT cycles + 3 RT cycles = 163 RT cycles.

The maximum percent difference between the receiver count and the

transmitter count of a slow 9-bit character with no errors is

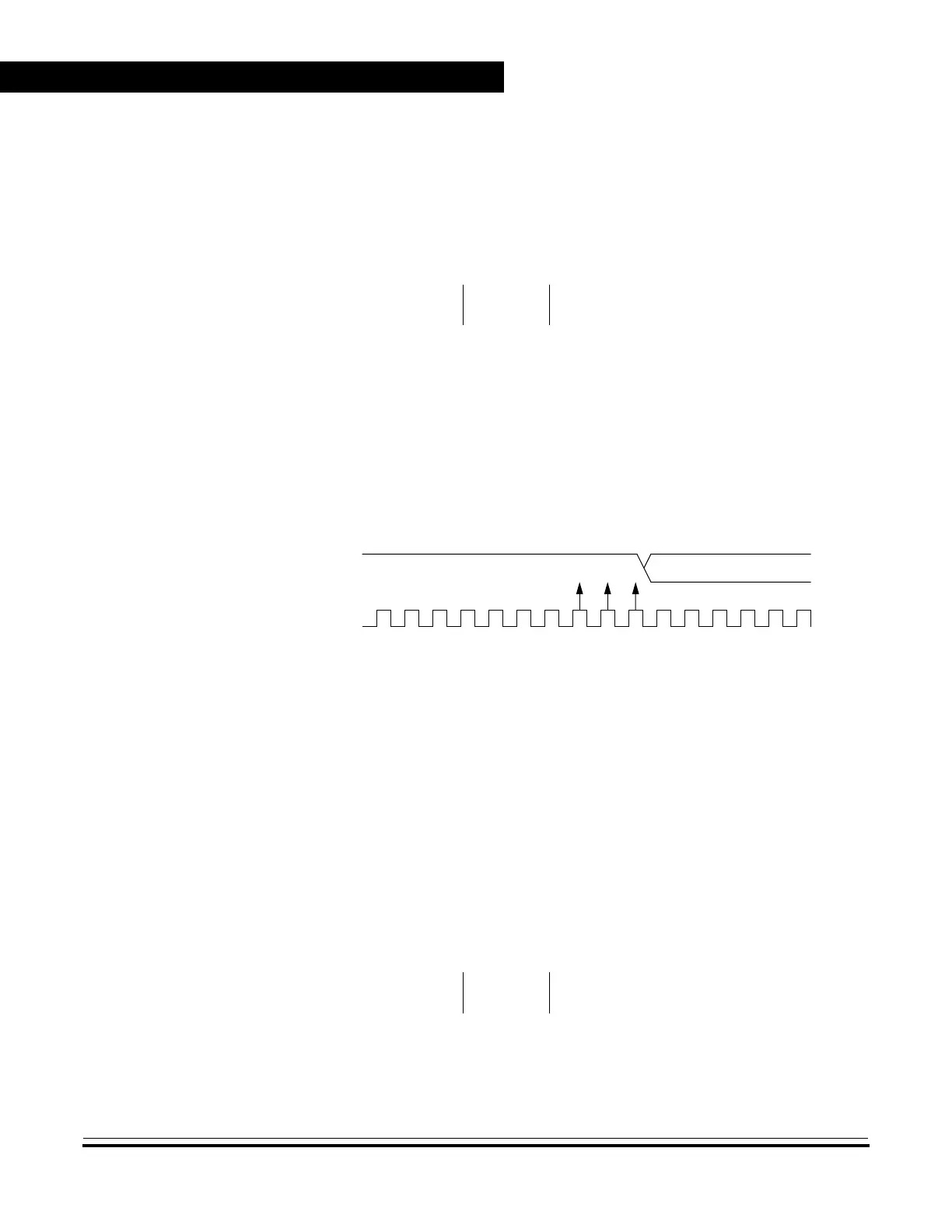

Fast Data Tolerance

Figure 15-8 shows how much a fast received character can be

misaligned without causing a noise error or a framing error. The fast stop

bit ends at RT10 instead of RT16 but is still there for the stop bit data

samples at RT8, RT9, and RT10.

Figure 15-8. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver

9 bit times × 16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 15-8, the receiver counts

154 RT cycles at the point when the count of the transmitting device is

10 bit times × 16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the

transmitter count of a fast 8-bit character with no errors is

170 163–

170

--------------------------

100× 4.12%=

IDLE OR NEXT CHARACTERSTOP

RT1

RT2

RT3

RT4

RT5

RT6

RT7

RT8

RT9

RT10

RT11

RT12

RT13

RT14

RT15

RT16

DATA

SAMPLES

RECEIVER

RT CLOCK

154 160–

154

--------------------------

100× 3.90%

˙

=

Loading...

Loading...