Monitor ROM (MON)

Technical Data MC68HC908AB32 — Rev. 1.0

166 Monitor ROM (MON) MOTOROLA

10.4.6 Baud Rate

With a 4.9152-MHz crystal and the PTC3 pin at logic 1 during reset, data

is transferred between the monitor and host at 4800 baud. If the PTC3

pin is at logic 0 during reset, the monitor baud rate is 9600. When the

CGM output, CGMOUT, is driven by the PLL, the baud rate is

determined by the MUL[7:4] bits in the PLL programming register (PPG).

(See Section 9. Clock Generator Module (CGM).)

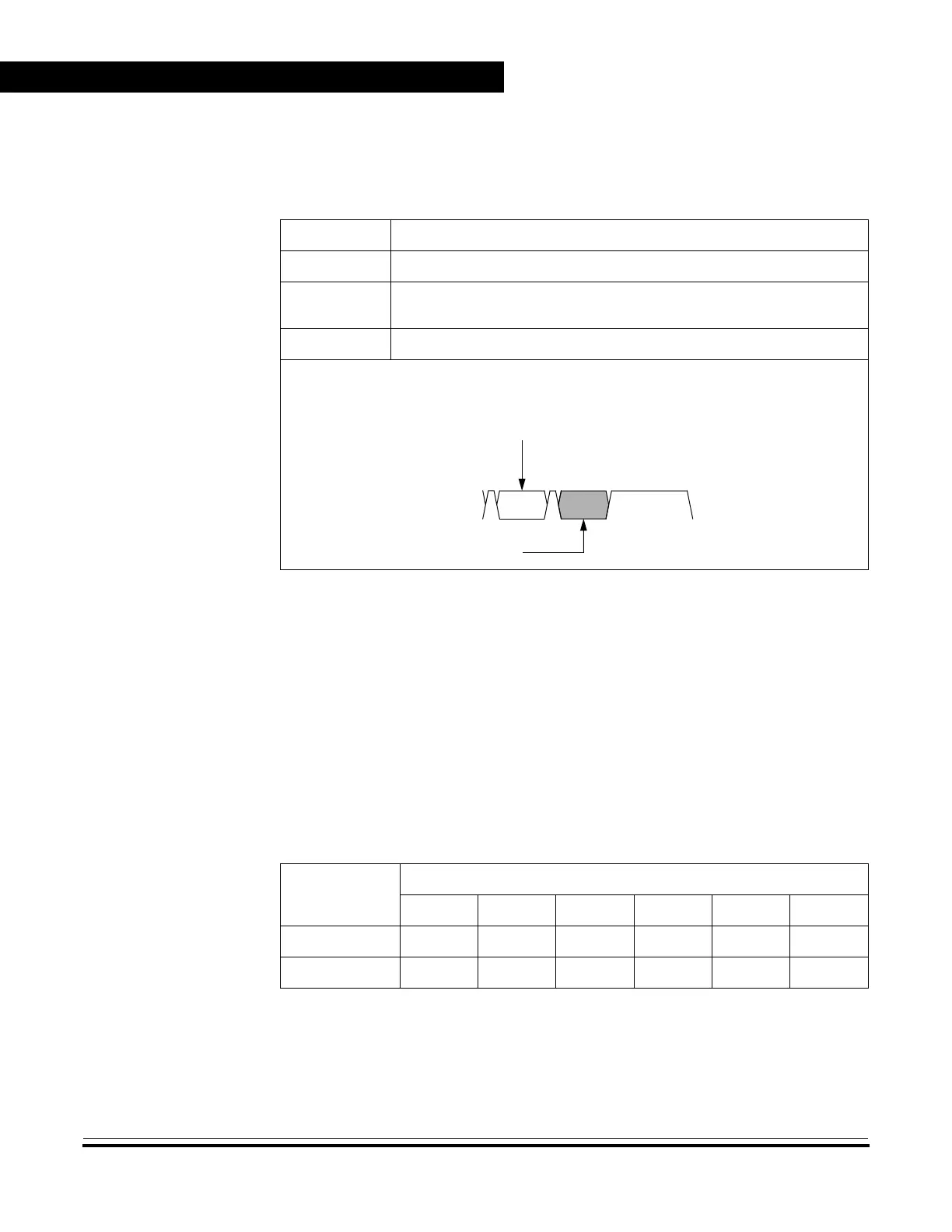

Table 10-8. RUN (Run User Program) Command

Description Executes RTI instruction

Operand None

Data

Returned

None

Opcode $28

Command Sequence

RUN

RUN

ECHO

SENT TO

MONITOR

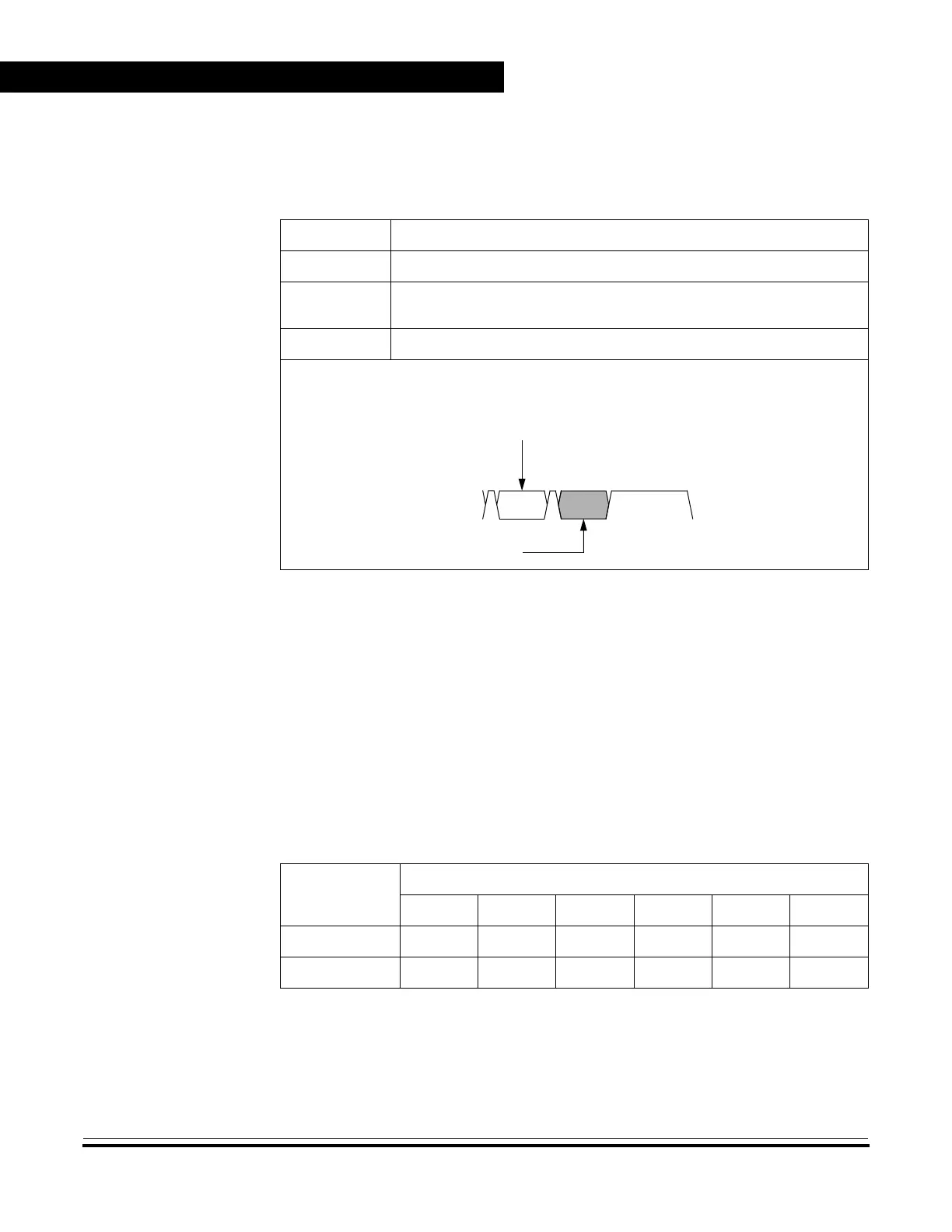

Table 10-9. Monitor Baud Rate Selection

Monitor

Baud Rate

VCO Frequency Multiplier (N)

123456

4.9152 MHz 4800 9600 14,400 19,200 24,000 28,800

4.194 MHz 4096 8192 12,288 16,384 20,480 24,576

Loading...

Loading...