14-45

IM 760401-01E

Communication Commands 2 (System of Commands Complying to the IEEE 488.2-1992 Standard)

14

Overview of Registers and Queues

Name Function Writing Reading

Status byte — Serial poll (RQS),

*STB?(MSS)

Service request Masks status byte. *SRE *SRE?

enable register

Standard event Event in the — *ESR?

register instrument (1)

Standard event Masks standard *ESE *ESE?

enable register event register.

Extended event Event in the — STATus:EESR?

register instrument (2)

Extended event Masks extended STATus:EESE STATus:EESE?

enable register event register.

Condition

Current instrument status

— STATus:CONDition?

register

Transition Extended event STATus:FILTer STATus:FILTer<x>

filter occurrence conditions <x>

Output queue

Stores response message All executable queues

to a query.

Error queue Stores error Nos. — STATus:ERRor?

and messages.

Registers and Queues which Affect the Status Byte

Registers which affect each bit of the status byte are

shown below.

Standard event register: Sets bit 5 (ESB) of status byte to “1” or “0”.

Output queue: Sets bit 4 (MAV) of status byte to “1” or “0”.

Extended event register: Sets bit 3 (EES) of status byte to “1” or “0”.

Error queue: Sets bit 2 (EAV) of status byte to “1” or “0”.

Enable Registers

Registers which mask a bit so that the bit does not

affect the status byte, even if the bit is set to “1,” are

shown below.

Status byte: Masks bits using the service request enable register.

Standard event register: Masks bits using the standard event enable register.

Extended event register: Masks bits using the extended event enable register.

Writing/Reading from Registers

The *ESE command is used to set bits in the standard

event enable register to “

1” or “0,” and the *ESR?

query is used to check whether bits in that register are

set to “

1” or “0.” For details of these commands, refer

to section 14.3.

14.4.2 Status Byte

Overview of Status Byte

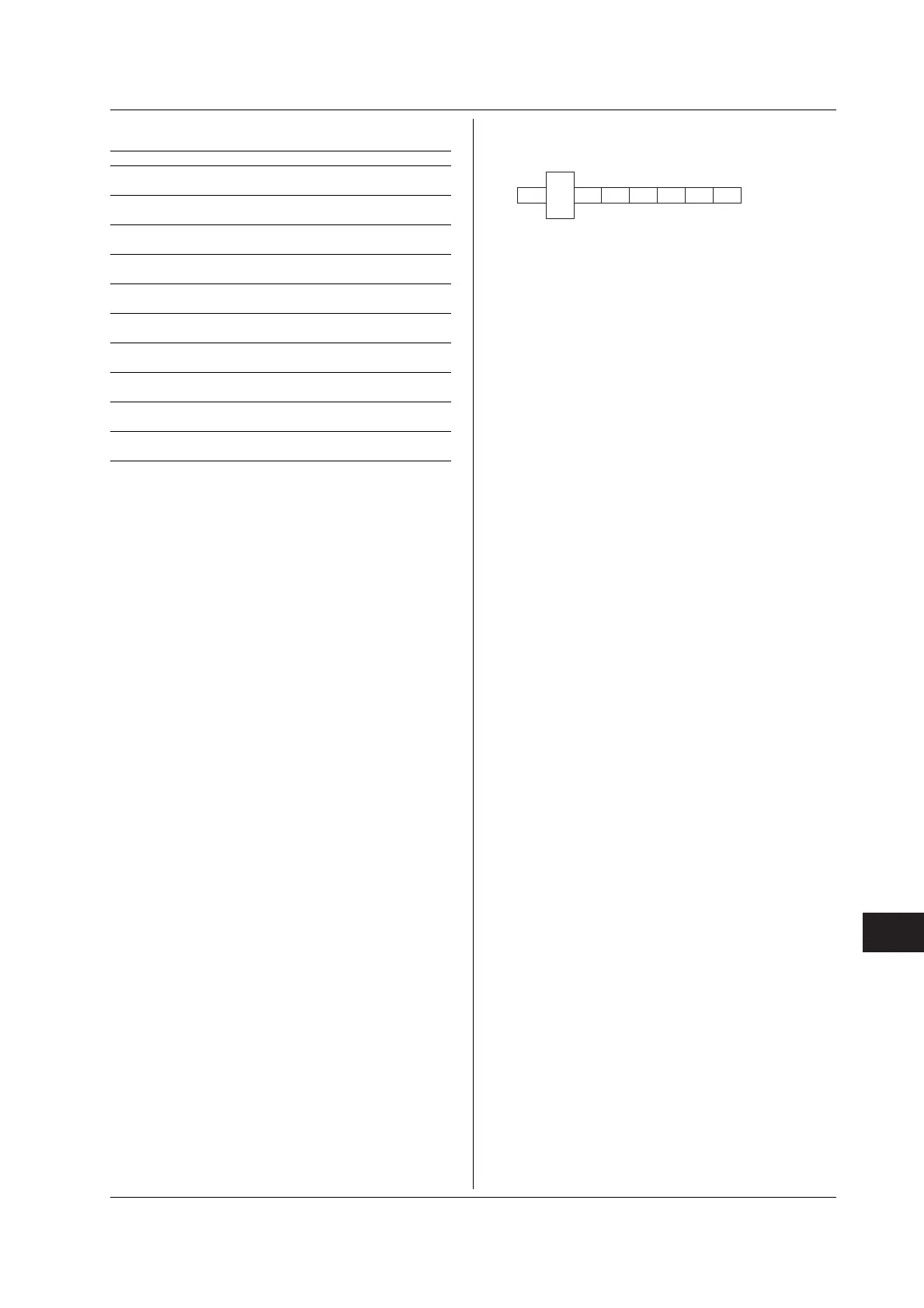

76ESB MAV EES EAV 1 0

RQS

MSS

Bits 0, 1 and 7

Not used (always “0”)

Bit 2 EAV (Error Available)

Set to “1” when the error queue is not empty, i.e. when

an error occurs. For details, refer to page 14-44.

Bit 3 EES (Extended Event Summary Bit)

Set to “1” when a logical AND of the extended event

register and the corresponding enable register is “1,”

i.e. when an event takes place in the instrument. Refer

to page 14-47.

Bit 4 MAV (Message Available)

Set to “

1” when the output queue is not empty, i.e.

when there is data which is to be output when an

inquiry is made. Refer to page 14-44.

Bit 5 ESB (Event Summary Bit)

Set to “1” when a logical AND of the standard event

register and the corresponding enable register is “1”,

i.e. when an event takes place in the instrument. Refer

to page 14-46.

Bit 6 RQS (Request Status)/MSS (Master Summary

Status )

MSS is set to “

1” when a logical AND of the status byte

(except for bit 6) and the service request enable

register is not “

0,” i.e. when the instrument is

requesting service from the controller.

RQS is set to “1” when MSS changes from “0” to “1,”

and is cleared when a serial poll is performed or when

MSS changes to “

0.”

Bit Masking

To mask a bit in the status byte so that it does not

cause an SRQ, set the corresponding bit of the service

request enable register to “0.”

For example, to mask bit 2 (EAV) so that no service

will be requested, even if an error occurs, set bit 2 of

the service request enable register to “

0.” This can be

done using the *SRE command. To query whether

each bit of the service request enable register is “

1” or

“0,” use *SRE?. For details of the *SRE command,

refer to 14.3.

14.4 Status Report

Loading...

Loading...