RL78/G13 CHAPTER 22 SAFETY FUNCTIONS

R01UH0146EJ0100 Rev.1.00 909

Sep 22, 2011

22.3.3 RAM parity error detection function

The IEC60730 standard mandates the checking of RAM data. A single-bit parity bit is therefore added to all 8-bit data

in the RL78/G13’s RAM. By using this RAM parity error detection function, the parity bit is appended when data is written,

and the parity is checked when the data is read. This function can also be used to trigger a reset when a parity error

occurs.

<Control register>

• RAM parity error control register (RPECTL)

This register is used to control parity error generation check bit and reset generation due to parity errors.

The RPECTL register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

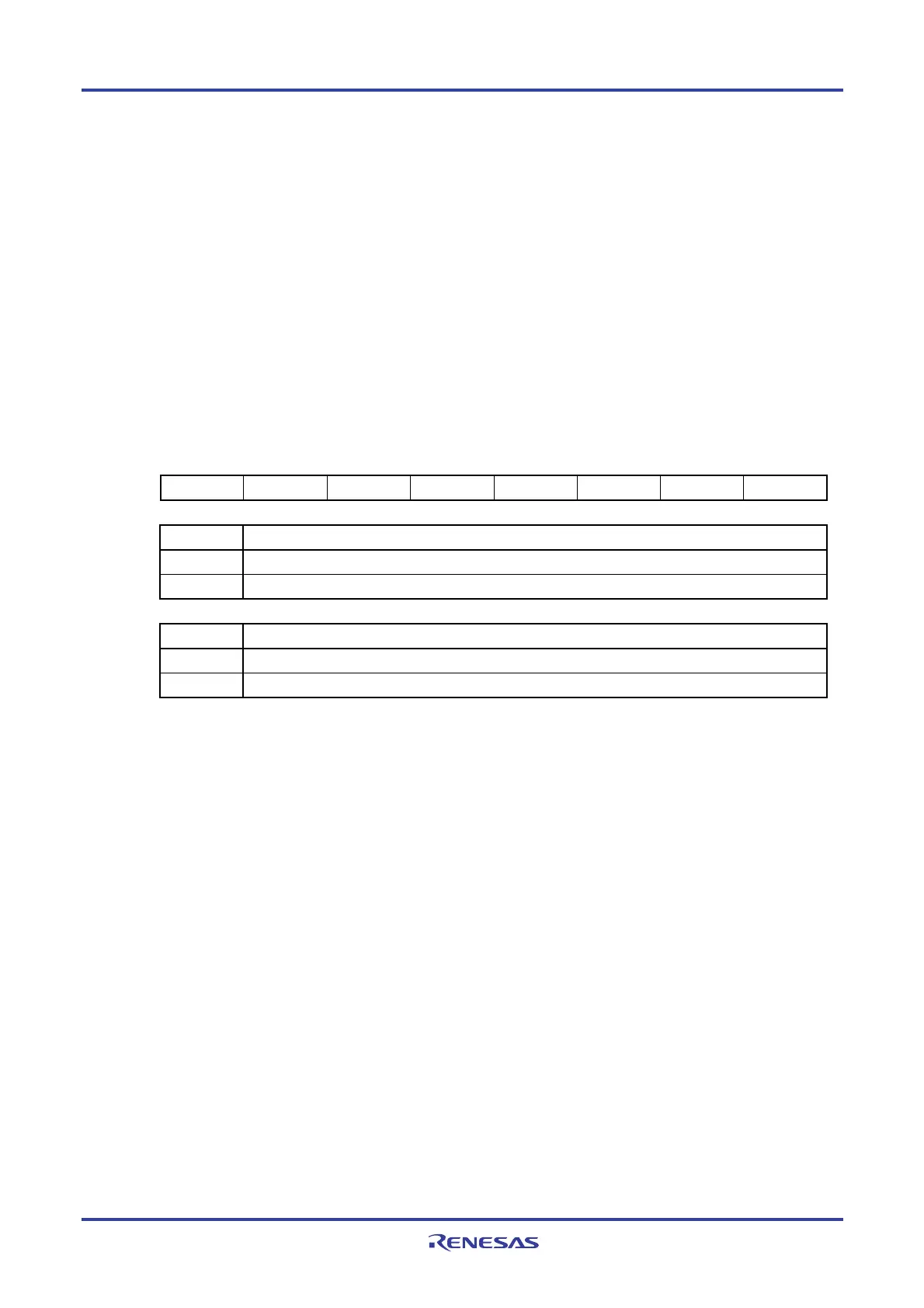

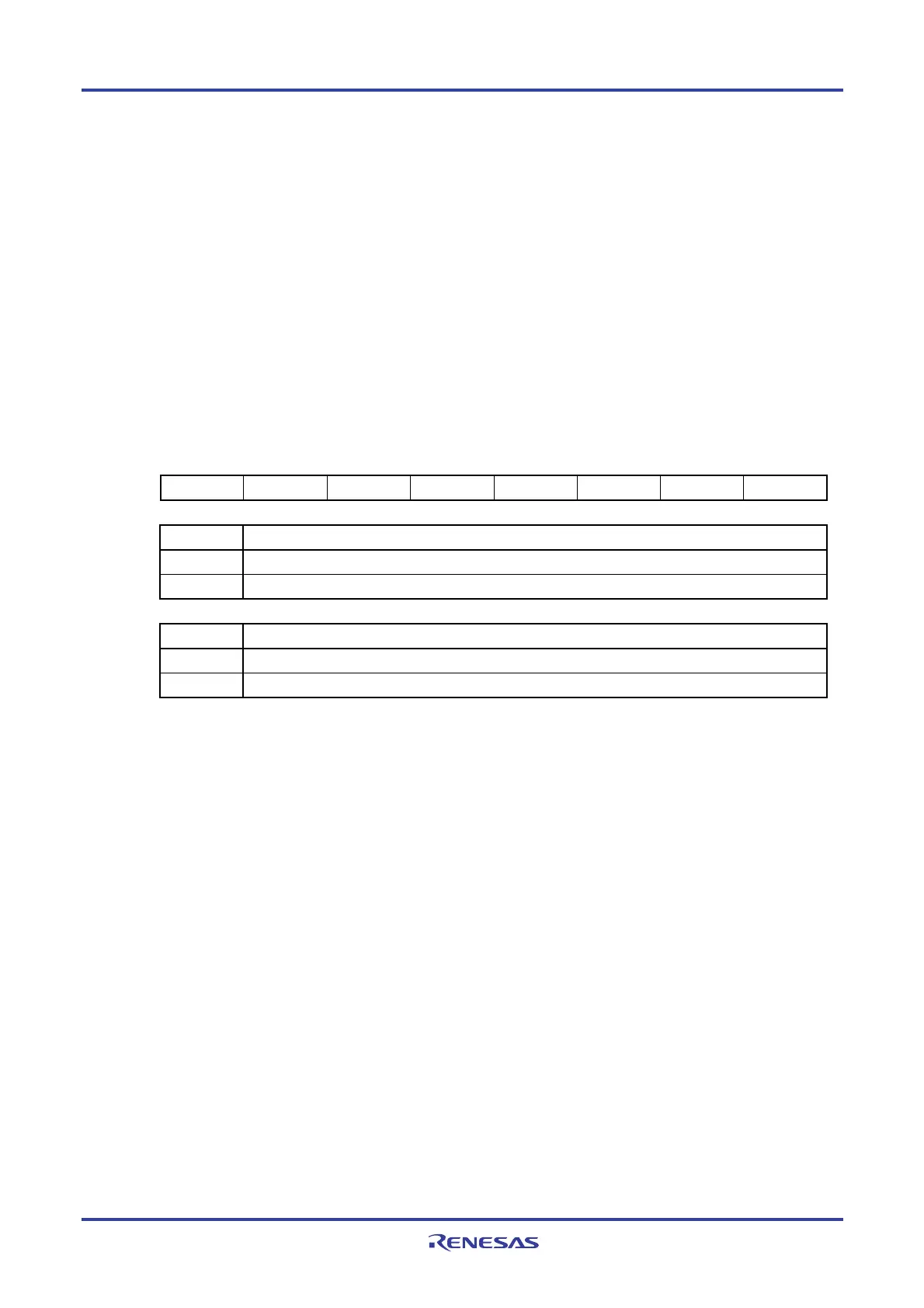

Figure 22-7. Format of RAM Parity Error Control Register (RPECTL)

Address: F00F5H After reset: 00H R/W

Symbol <7> 6 5 4 3 2 1 <0>

RPECTL RPERDIS 0 0 0 0 0 0 RPEF

RPERDIS Parity error reset mask flag

0 Enable parity error resets.

1 Disable parity error resets.

RPEF Parity error status flag

0 No parity error has occurred.

1 A parity error has occurred.

Caution An instruction code fetched from RAM is not subject to parity error detection while it is being

executed. However, the RL78’s CPU executes lookahead due to the pipeline operation, the CPU

might read an uninitialized RAM area that is allocated beyond the RAM used, which causes a RAM

parity error. Therefore, when enabling RAM parity error resets (RPERDIS = 1), be sure to initialize

the used RAM area + 10 bytes. When using the self-programming function while RAM parity error

resets are enabled, be sure to initialize the RAM area to overwrite + 10 bytes before overwriting.

The data read by the instruction is subject to parity error detection.

Remarks 1. The RAM parity check is always on, and the result can be confirmed by checking the PREF flag.

2. The parity error reset is enabled by default (RPERDIS = 0).

Even if the parity error reset is disabled (RPERDIS = 1), the RPEF flag will be set (1) if a parity error

occurs.

3. The RPEF flag is set (1) by RAM parity errors and cleared (0) by writing 0 to it or by any reset source.

When RPEF = 1, the value is retained even if RAM for which no parity error has occurred is read.

Loading...

Loading...