VCU118 Board User Guide 26

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Chapter 3: Board Component Descriptions

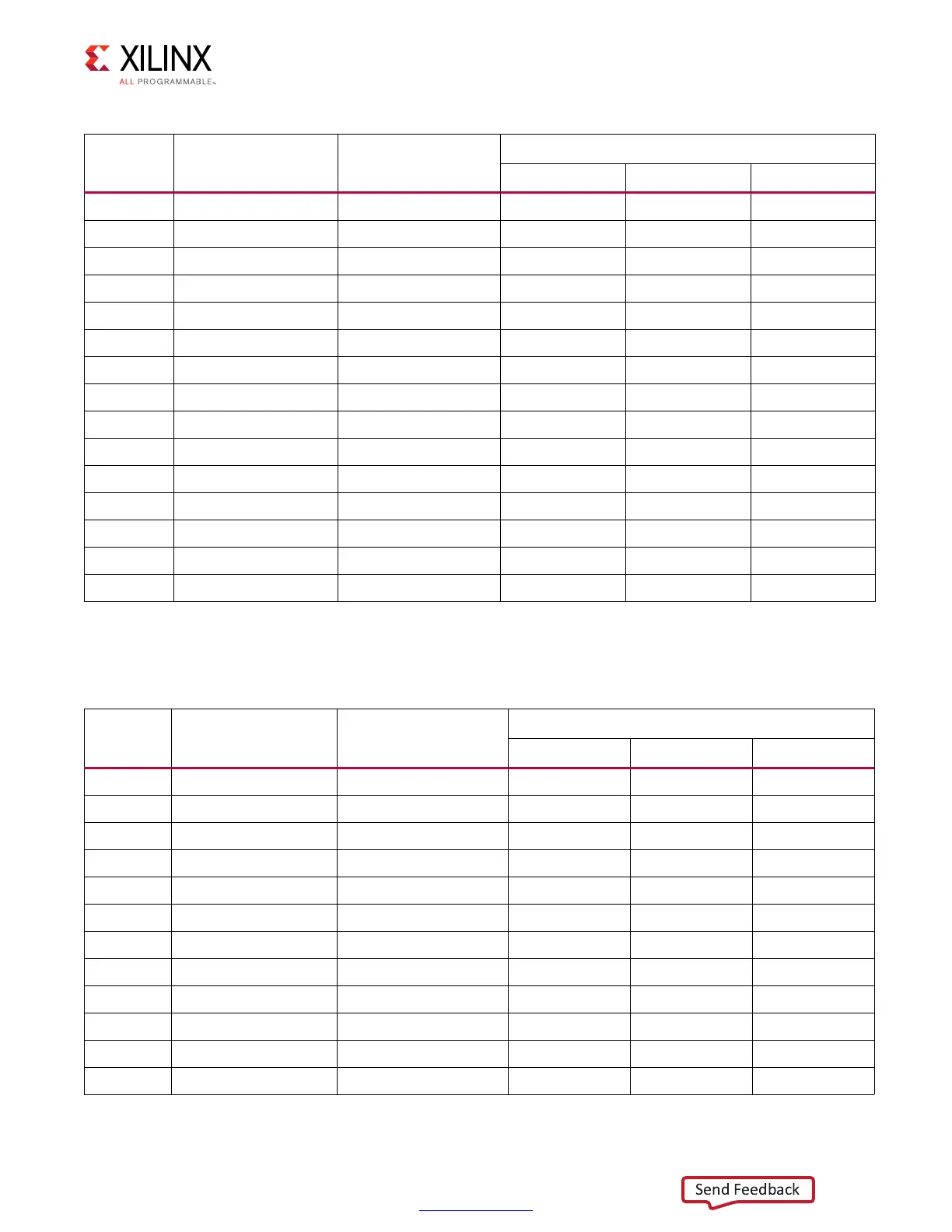

The connections between the C2 80-bit interface DDR4 component memories (U135-U139)

and XCVU9P banks 40, 41, and 42 are listed in Table 3-3.

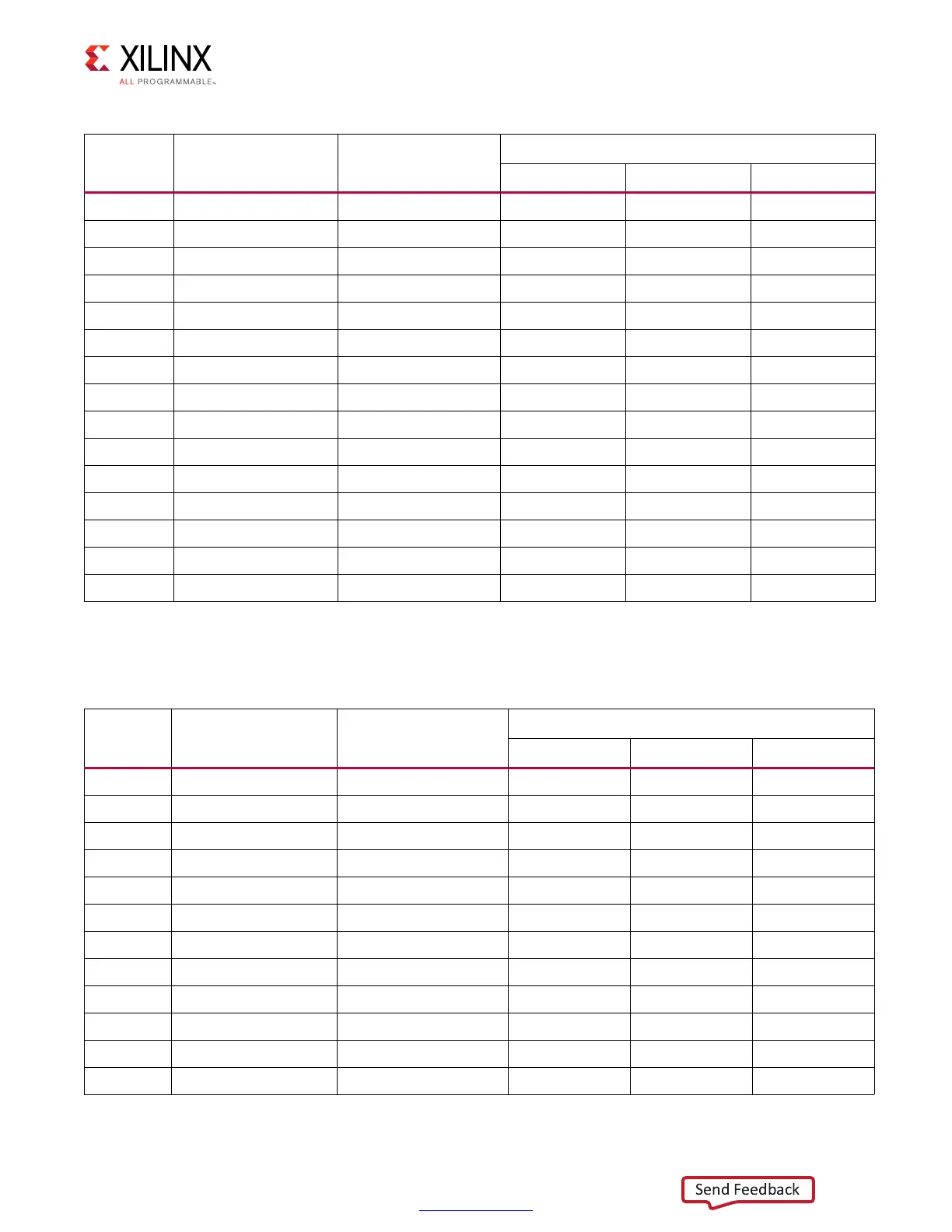

G13 DDR4_C1_BA1 SSTL12_DCI N8 BA1 U60-U64

H13 DDR4_C1_BG0 SSTL12_DCI M2 BG0 U60-U64

H14 DDR4_C1_A14_WE_B SSTL12_DCI L2 WE_B/A14 U60-U64

H15 DDR4_C1_A15_CAS_B SSTL12_DCI M8 CAS_B_A15 U60-U64

F15 DDR4_C1_A16_RAS_B SSTL12_DCI L8 RAS_B/A16 U60-U64

F14 DDR4_C1_CK_T DIFF_SSTL12_DCI K7 CK_T U60-U64

E14 DDR4_C1_CK_C DIFF_SSTL12_DCI K8 CK_C U60-U64

A10 DDR4_C1_CKE SSTL12_DCI K2 CKE U60-U64

E13 DDR4_C1_ACT_B SSTL12_DCI L3 ACT_B U60-U64

G10 DDR4_C1_PAR SSTL12_DCI T3 PAR U60-U64

C8 DDR4_C1_ODT SSTL12_DCI K3 ODT U60-U64

F13 DDR4_C1_CS_B SSTL12_DCI L7 CS_B U60-U64

R17 DDR4_C1_ALERT_B SSTL12_DCI P9 ALERT_B U60-U64

N20 DDR4_C1_RESET_B LVCMOS12 P1 RESET_B U60-U64

A20 DDR4_C1_TEN SSTL12_DCI N9 TEN U60-U64

Table 3-2: DDR4 Memory 80-bit I/F C1 to FPGA U1 Banks 71, 72, and 73 (Cont’d)

FPGA (U1)

Pin

Schematic Net Name I/O Standard

Component Memory

Pin # Pin Name Ref. Des.

Table 3-3: DDR4 Memory 80-bit I/F C2 to FPGA U1 Banks 40, 41, and 42

FPGA (U1)

Pin

Schematic Net Name I/O Standard

Component Memory

Pin # Pin Name Ref. Des.

BD30 DDR4_C2_DQ0 POD12_DCI G2 DQL0 U135

BE30 DDR4_C2_DQ1 POD12_DCI F7 DQL1 U135

BD32 DDR4_C2_DQ2 POD12_DCI H3 DQL2 U135

BE33 DDR4_C2_DQ3 POD12_DCI H7 DQL3 U135

BC33 DDR4_C2_DQ4 POD12_DCI H2 DQL4 U135

BD33 DDR4_C2_DQ5 POD12_DCI H8 DQL5 U135

BC31 DDR4_C2_DQ6 POD12_DCI J3 DQL6 U135

BD31 DDR4_C2_DQ7 POD12_DCI J7 DQL7 U135

BA32 DDR4_C2_DQ8 POD12_DCI A3 DQU0 U135

BB33 DDR4_C2_DQ9 POD12_DCI B8 DQU1 U135

BA30 DDR4_C2_DQ10 POD12_DCI C3 DQU2 U135

BA31 DDR4_C2_DQ11 POD12_DCI C7 DQU3 U135

Loading...

Loading...