VCU118 Board User Guide 65

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Chapter 3: Board Component Descriptions

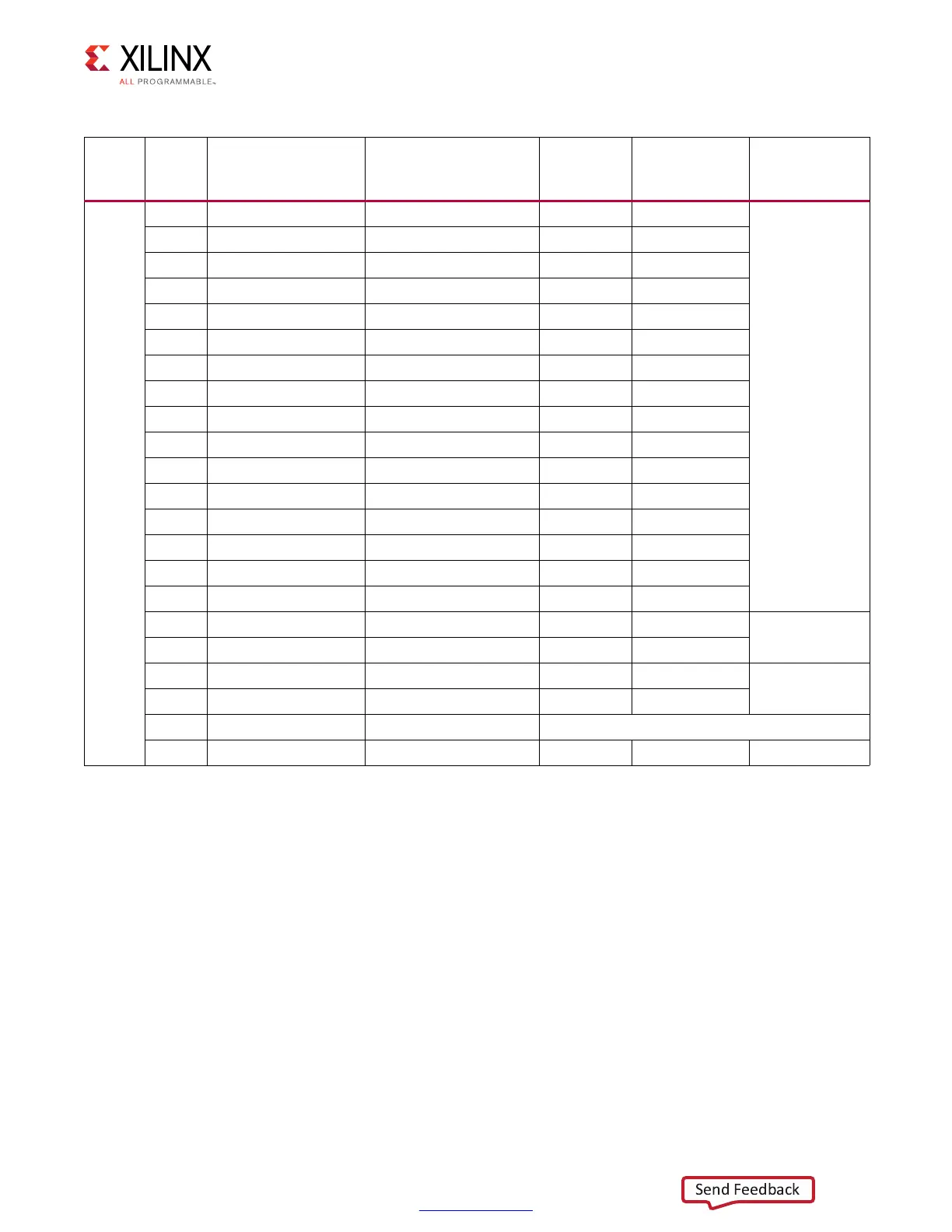

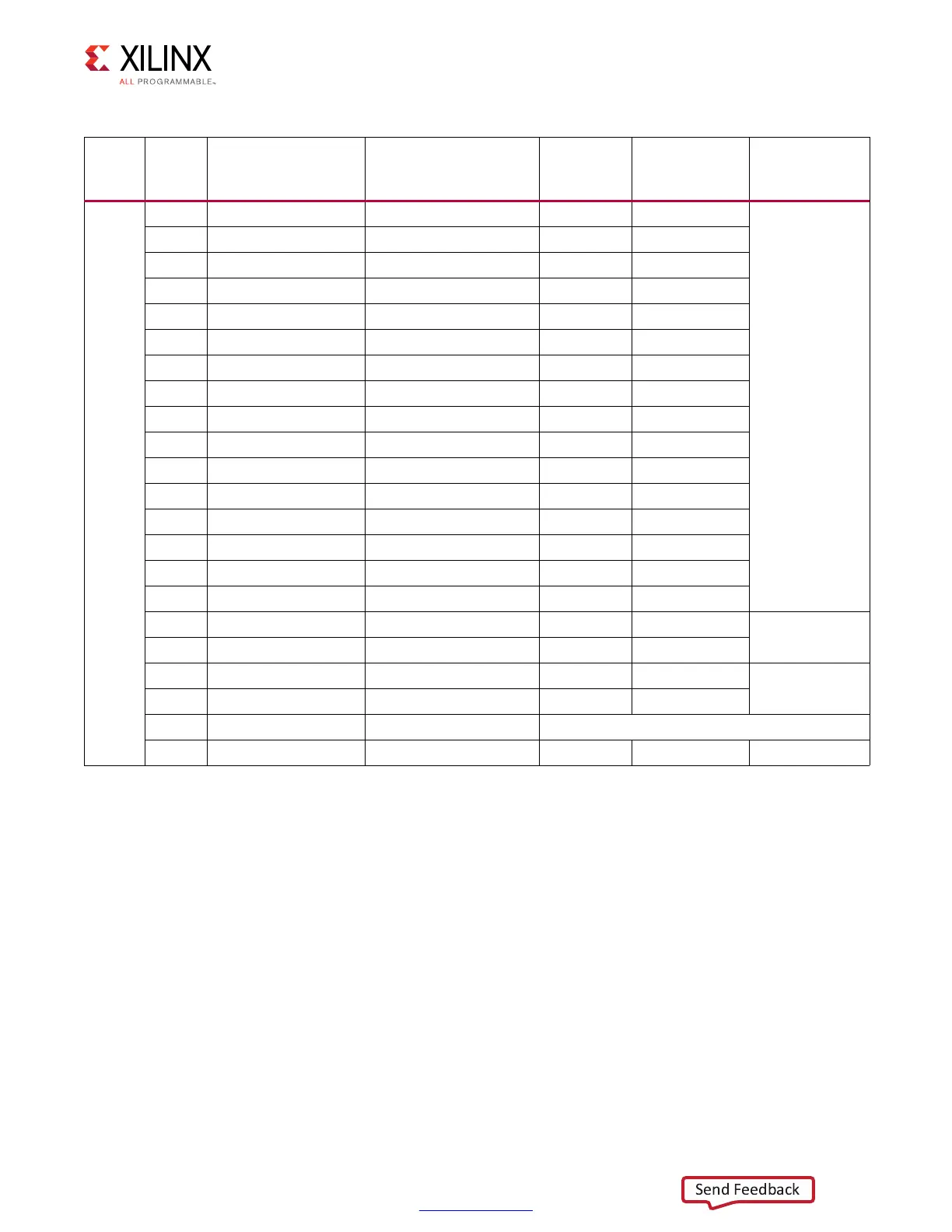

Table 3-18: VCU118 FPGA U1 GTY Transceiver Bank 231 Connections

MGT

Bank

FPGA

(U1)

Pin

FPGA (U1) Pin Name Schematic Net Name

Connected

Pin

Connected Pin

Name

Connected

Device

GTY

Bank

231

V7 MGTYTXP0_231 QSFP1_TX1_P 36 TX1P

QSFP1 U145

V6 MGTYTXN0_231 QSFP1_TX1_N 37 TX1N

Y2 MGTYRXP0_231 QSFP1_RX1_P 17 RX1P

Y1 MGTYRXN0_231 QSFP1_RX1_N 18 RX1N

T7 MGTYTXP1_231 QSFP1_TX2_P 3 TX2P

T6 MGTYTXN1_231 QSFP1_TX2_N 2 TX2N

W4 MGTYRXP1_231 QSFP1_RX2_P 22 RX2P

W3 MGTYRXN1_231 QSFP1_RX2_N 21 RX2N

P7 MGTYTXP2_231 QSFP1_TX3_P 33 TX3P

P6 MGTYTXN2_231 QSFP1_TX3_N 34 TX3N

V2 MGTYRXP2_231 QSFP1_RX3_P 14 RX3P

V1 MGTYRXN2_231 QSFP1_RX3_N 15 RX3N

M7 MGTYTXP3_231 QSFP1_TX4_P 6 TX4P

M6 MGTYTXN3_231 QSFP1_TX4_N 5 TX4N

U4 MGTYRXP3_231 QSFP1_RX4_P 25 RX4P

U3 MGTYRXN3_231 QSFP1_RX4_N 24 RX4N

W9 MGTREFCLK0P_231 QSFP_SI570_CLOCK_C_P 4 OUT

U38 SI570 I

2

C

prog. osc.

W8 MGTREFCLK0N_231 QSFP_SI570_CLOCK_C_N 5 OUT_B

U9 MGTREFCLK1P_231 SI5328_CLOCK1_C_P 28 CLKOUT1_P

U57 SI5328B

jitter atten.

U8 MGTREFCLK1N_231 SI5328_CLOCK1_C_N 29 CLKOUT1_N

A4 MGTRREF_RN MGTRREF_231 R1326.1 100Ω 1% P/U to MGTAVTT_FPGA

A5 MGTAVTTRCAL_RN MGTAVTT_FPGA NA NA NA

Loading...

Loading...