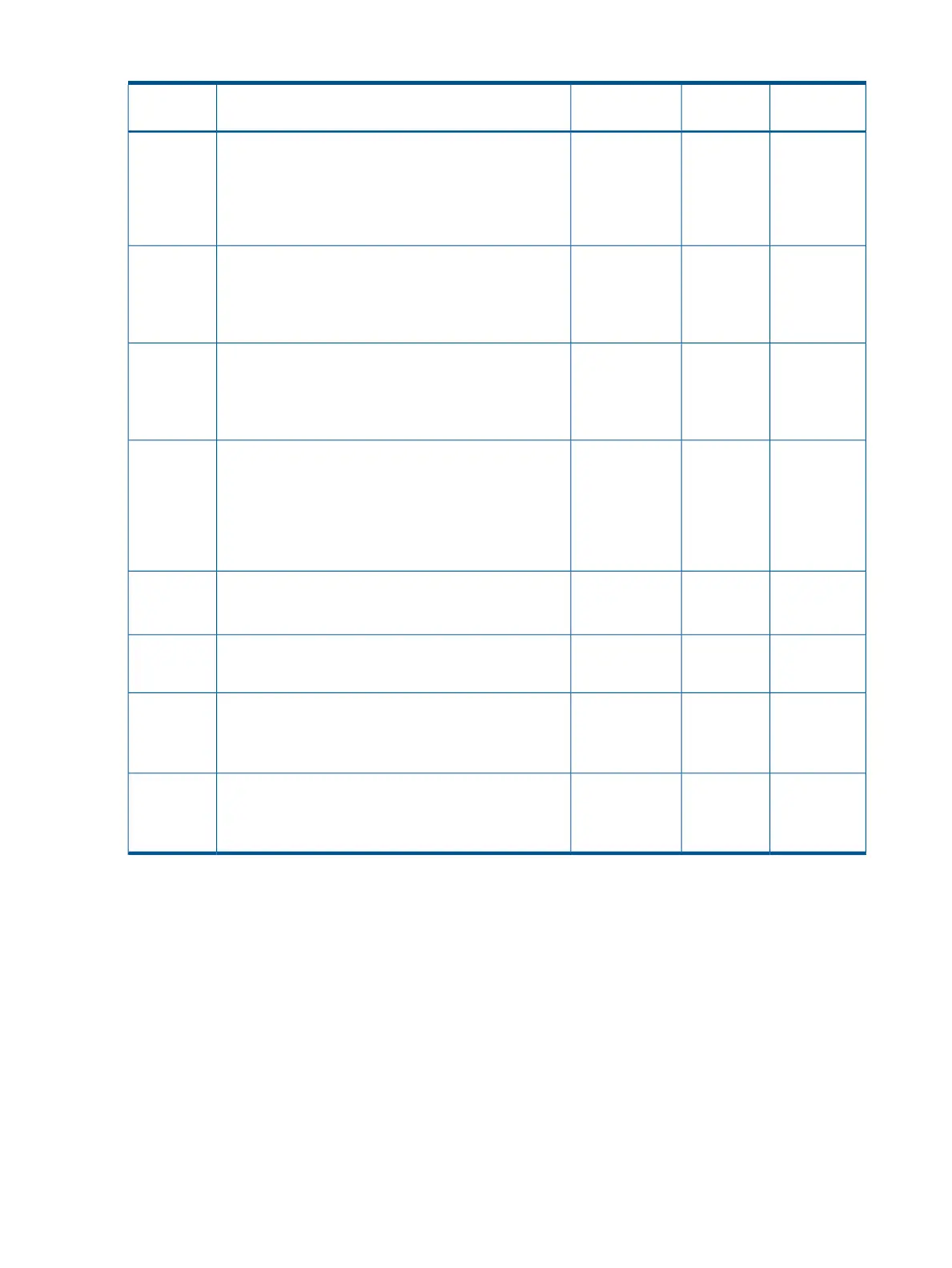

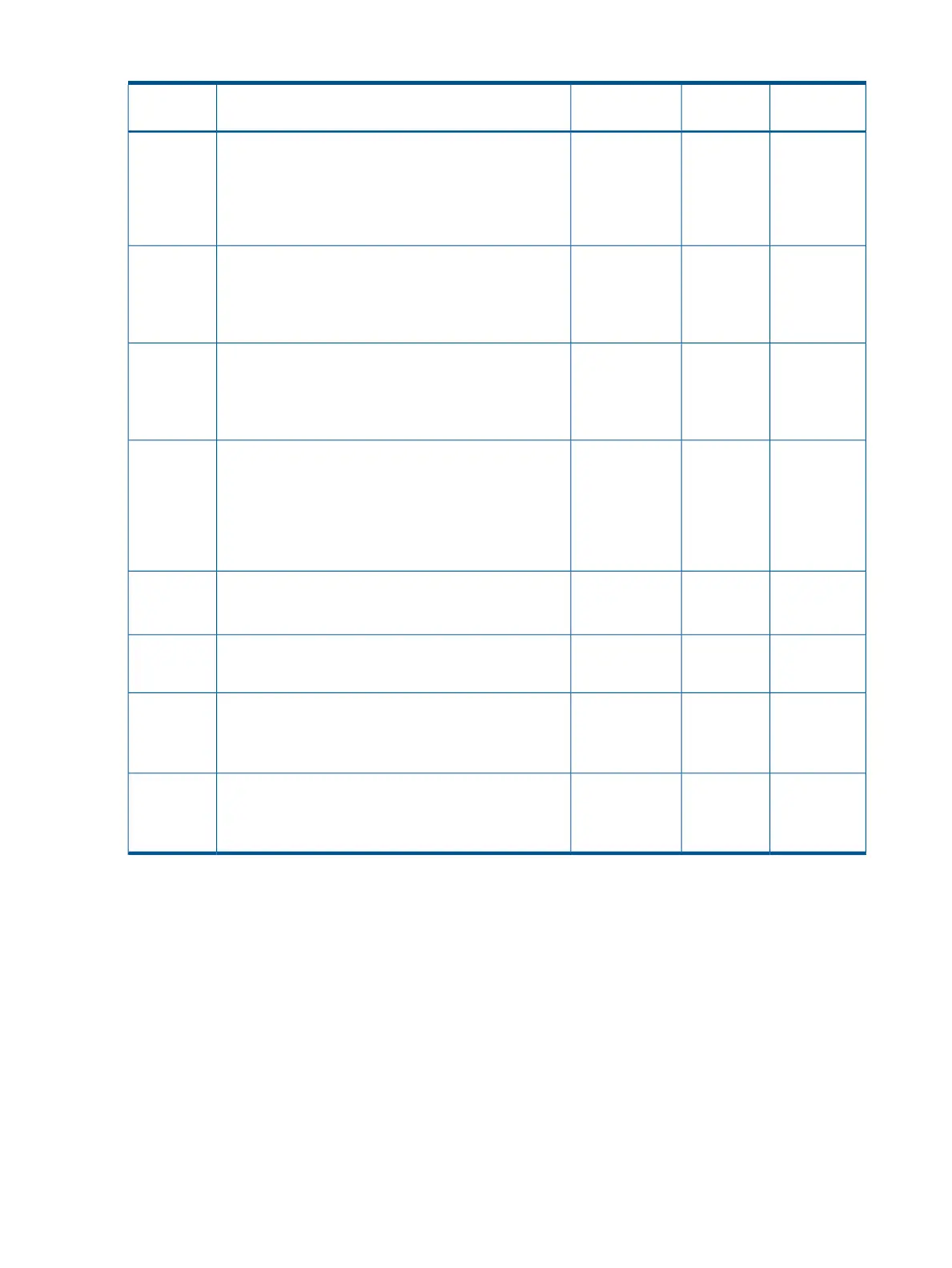

Table 27 Processor events that might illuminate SID LEDs (continued)

NotesSourceCauseSample IPMI EventsDiagnostic

LEDs

SFWA watchdog

timer expired

Type E0h, 745d:26d

BOOT_FINAL_RENDEZ_WATCHDOG_FAIL

Processor

and determined

that a monarch

processor is not

responding.

Bad or slow

processor

SFWA logical

processor

Type E0h, 83d:26d

BOOT_RENDEZ_FAILURE

Processors

(thread)

rendezvous

failure

SFWThe logical

monarch

Type E0h, 67d:26d

BOOT_MONARCH_TIMEOUT

Processors

processor

(thread) has

timed out

SFWA logical slave

processor

Type E0h, 57d:26d

BOOT_INCOMPATIBLE_SLAVE

Processors

(thread) is

incompatible

with logical

monarch

processor

SFWProcessor PAL

incompatible

with processor

Type E0h, 56d:26d

BOOT_INCOMPATIBLE_ PAL

Processor

SFWA processor

failed

Type E0h, 34d:26d

BOOT_CPU_FAILED

Processors

SFWA logical

processor

Type E0h, 33d:26d

BOOT_CPU_EARLY_TEST_FAIL

Processors

(thread) failed

early self test

Possible

seating or

iLO MPNo physical

processor cores

present

Type 02h, 25h:71h:80h

MISSING_FRU_DEVICE

Processors

failed

processor

Troubleshooting the server memory

Memory DIMM load order

For a minimally loaded server, two equal-size DIMMs must be installed in the DIMM slots. For more

information, see Table 6 (page 47).

Memory subsystem behaviors

The processor and the integrated memory controller provides increased reliability of DIMMs. The

memory controller built into the 9300 series processor doubles memory rank error correction from

4 bytes to 8 bytes of a 128 byte cache line, during cache line misses initiated by processor cache

controllers and by DMA operations initiated by I/O devices. This feature is called double DRAM

sparing, since 2 of 72 DRAMs in any DIMM pair can fail without any loss of server performance.

Corrective action, such as DIMM/memory expander replacement, is required when a threshold is

reached for multiple double-byte errors from one or more DIMMs in the same rank. And when any

uncorrectable memory error (more than 2 bytes) or when no pair of like DIMMs is loaded in rank

82 Troubleshooting

Loading...

Loading...